US009020027B2

# (12) United States Patent

# Staszewski et al.

## (54) INTEGRATED CIRCUIT, COMMUNICATION UNIT AND METHOD FOR IMPROVED AMPLITUDE RESOLUTION OF AN RF-DAC

- (71) Applicant: MediaTek Singapore Pte. Ltd., Singapore (SG)

- (72) Inventors: Robert Bogdan Staszewski, Delft (NL); Min Park, Stanford, CA (US)

- (73) Assignee: MediaTek Singapore Pte. Ltd., Singapore (SG)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

This patent is subject to a terminal disclaimer.

- (21) Appl. No.: 14/162,749

- (22) Filed: Jan. 24, 2014

#### (65) **Prior Publication Data**

US 2014/0185663 A1 Jul. 3, 2014

#### **Related U.S. Application Data**

- (63) Continuation of application No. 13/018,394, filed on Jan. 31, 2011, now Pat. No. 8,675,725.

- (60) Provisional application No. 61/329,159, filed on Apr. 29, 2010, provisional application No. 61/407,186, filed on Oct. 27, 2010.

- (51) Int. Cl.

| H03K 7/08  | (2006.01)   |  |

|------------|-------------|--|

| H03F 3/217 | (2006.01)   |  |

|            | (Continued) |  |

# (10) Patent No.: US 9,020,027 B2

# (45) **Date of Patent:** \*Apr. 28, 2015

## (56) **References Cited**

#### U.S. PATENT DOCUMENTS

| 6,141,541 A  | 10/2000     | Midya      |  |

|--------------|-------------|------------|--|

| 6,924,681 B2 | 8/2005      | Staszewski |  |

|              | (Continued) |            |  |

#### FOREIGN PATENT DOCUMENTS

| CN | 101036359 | Α | 9/2007 |

|----|-----------|---|--------|

| JP | H07226635 | А | 8/1995 |

(Continued)

#### OTHER PUBLICATIONS

Staszewski, R.B. et al., "Sigma-delta noise shaping for digital-tofrequency and digital-to-RF-amplitude conversion", System-on-Chip for Real-Time Applications, 2005 IEEE Computer Society, Proceedings of the 9th International Database Engineering & Application Symposium (IDEAS'05). Fifth International Workshop, Jul. 20-24, 2005.

#### (Continued)

Primary Examiner — Lihong Yu

(74) Attorney, Agent, or Firm - Winston Hsu; Scott Margo

## (57) **ABSTRACT**

An integrated circuit includes: a digitally-controlled power generation stage for converting an input signal to a radio frequency (RF) carrier, the digitally-controlled power generation stage including a plurality of selectable switching devices capable of adjusting an envelope of the RF carrier; and a pulse width modulator (PWM) generator arranged to generate a PWM control signal according to a fractional word and operably coupleable to the plurality of selectable switching devices of the digitally-controlled power generation stage; wherein the PWM generator inputs the PWM control signal to a subset of the plurality of the selectable switching devices such that a PWM signal adjusts the envelope of the RF carrier output from the digitally-controlled power generation stage.

#### 22 Claims, 30 Drawing Sheets

(51) Int. Cl.

| • / | Inte Ch    |           |

|-----|------------|-----------|

|     | H03M 1/68  | (2006.01) |

|     | H04B 14/02 | (2006.01) |

|     | H03M 1/74  | (2006.01) |

|     | H03M 1/82  | (2006.01) |

# (56) **References Cited**

#### U.S. PATENT DOCUMENTS

| 7,667,511<br>7,693,498<br>8,675,725 | B2 | 4/2010  | Staszewski<br>Rofougaran<br>Staszewski et al |

|-------------------------------------|----|---------|----------------------------------------------|

| 2002/0180547                        | A1 | 12/2002 | Staszewski                                   |

| 2006/0284673                        | A1 | 12/2006 | Peruzzi                                      |

| 2006/0291589                        | A1 | 12/2006 | Eliezer                                      |

| 2009/0218995                        | A1 | 9/2009  | Ahn                                          |

#### FOREIGN PATENT DOCUMENTS

| JP | H10126159  | Α | 5/1998 |

|----|------------|---|--------|

| JP | 2002158544 | Α | 5/2002 |

#### OTHER PUBLICATIONS

Eloranta, A Multimode Transmitter in 0.13 um CMOS Using Direct-Digital RF Modulator, IEEE Journal of Solid-State Circuits, pp. 2774-2784, vol. 42, No. 12, Dec. 2007.

Jerng, A Wideband Delta-Sigma Digital-RF Modulator for High Data Rate Transmitters, IEEE Journal of Solid-State Circuits, pp. 1710-1722, vol. 42, No. 8, Aug. 2007.

Mehta, An Efficient Linearization Scheme for a Digital Polar EDGE Transmitter, IEEE Transactions on Circuits and Systems-II:Express Briefs, pp. 193-197, vol. 57, No. 3, Mar. 2010. Meninger, A Fractional-N Frequency Synthesizer Architecture Utilizing a Mismatch Compensated PFD/DAC Structure for Reduced Quantization-Induced Phase Noise, IEEE Transactions on Circuits and Systems-II:Analog and Digital Signal Processing, pp. 839-849, vol. 50, No. 11, Nov. 2003.

Park, A Time-Domain Resolution Improvement of an RF-DAC, IEEE Transactions on Circuits and Systems-II:Express Briefs, pp. 517-521, vol. 57, No. 7, Jul. 2010.

Staszewski, All-Digital PLL and Transmitter for Mobile Phones, IEEE Journal of Solid-State Circuits, pp. 2469-2482, vol. 40, No. 12, Dec. 2005.

Staszewski, Just-In-Time Gain Estimation of an RF Digitally-Controlled Oscillator for Digital Direct Frequency Modulation, IEEE Transactions on Circuits and Systems-II:Analog and Digital Signal Processing, pp. 887-892, vol. 50, No. 11, Nov. 2003.

Mehta, A 0.8mm2 All-Digital SAW-Less Polar Transmitter in 65nm EDGE Soc, pp. 58-59, Figure 3.2.7, ISSCC 2010/Session 3/Cellular Techniques/3.2, Feb. 8, 2010.

Nielsen, An RF Pulse Width Modulator for Switch-Mode Power Amplification of Varying Envelope Signals, pp. 277-280, 2007 Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, Jan. 2007.

Perrott, Fast and Accurate Behavioral Simulation of Fractional-N Frequency Synthesizers and other PLL/DLL Circuits, pp. 498-503, 39th Design Automation Conference, 2002, Jun. 2002.

M.O. Hawksford, "Linearization of Multilevel, Multiwidth Digital PWM with Applications in Digital-to-Analog Conversion", Journal of the Audio Engineering Society, Oct. 1995, pp. 787-798, vol. 43, No. 10, Audio Engineering Society, England.

\* cited by examiner

FIG. 2 Related Art

**FIG.** 5

**FIG.** 6

**FIG. 8**

FIG. 9

FIG. 11

FIG. 12

FIG. 13

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22

FIG. 24

FIG. 25

FIG. 26

FIG. 28

FIG. 33

FIG. 34

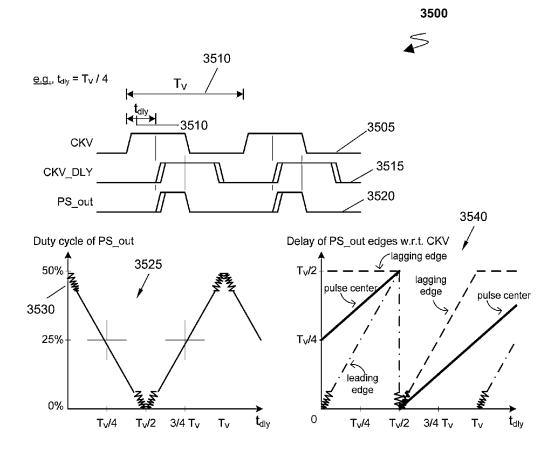

FIG. 35

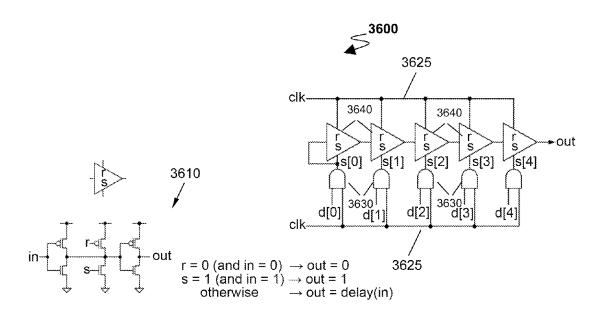

FIG. 36

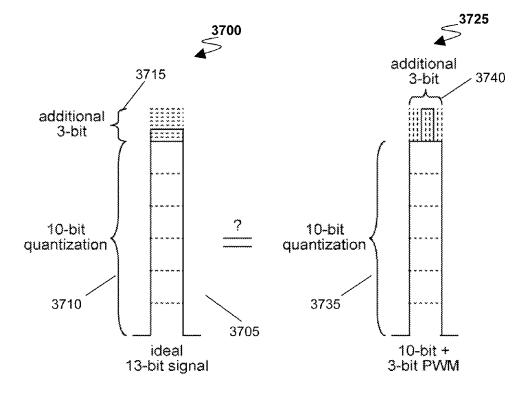

FIG. 37

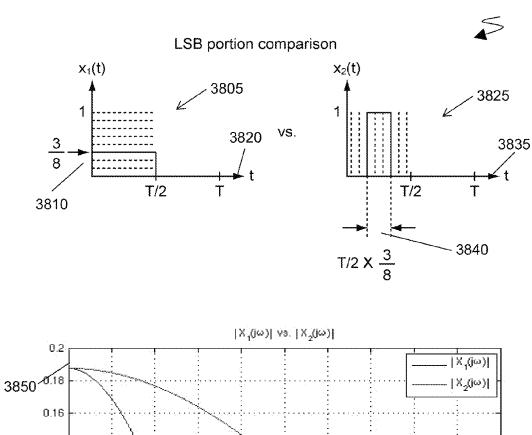

3800

5

FIG. 38

FIG. 39

5

# INTEGRATED CIRCUIT, COMMUNICATION UNIT AND METHOD FOR IMPROVED AMPLITUDE RESOLUTION OF AN RF-DAC

#### CROSS REFERENCE TO RELATED APPLICATIONS

This application is a continuation of co-pending U.S. patent application Ser. No. 13/018,394 (filed on Jan. 31, 2011), which claims the benefit of U.S. provisional applica- <sup>10</sup> tion No. 61/329,159 (filed on Apr. 29, 2010) and U.S. provisional application No. 61/407,186 (filed on Oct. 27, 2010), the contents of which are incorporated herein by reference.

#### BACKGROUND

The field of this invention relates to radio-frequency digital-to-amplitude converter(s) (RF-DAC(s). The invention is applicable to, but not limited to, radio-frequency digital-toamplitude converter(s) (RF-DAC(s)) employing pulse width 20 modulation.

One of the most important radio frequency (RF) architectural/circuit changes in the last decade has been the digitization of RF transceivers, such that digital functionality in the RF domain is now a key aspect for most wireless applications. 25 Thus, for low-cost and low-power wireless devices, systemon-chip (SoC) integration of RF circuits with digital circuits has proven to be popular. One example of this is in digital RF transmitters, which now comprise digital application specific integrated circuit (ASIC) cells and one or more radio-frequency digital-to-amplitude converter(s) (RF-DAC(s)).

Some recent publications on RF transmitters have shown that employing an RF-DAC can make RF SoC implementation easier, for example R. Staszewski, et al. "All-digital PLL and transmitter for mobile phones", published in IEEE J. 35 Solid-State Circuits, vol. 40, no. 12, pp 2469-2482, December 2005 [1], J. Mehta, et al. "A 0.8 mm2 11-digital SAW-less polar transmitter in 65 nm EDGE SoC", published in Proc. of IEEE Solid-State Circuits Conf, pp 58-59, December 2010 [2], A. Jerng, et al. "A wideband sigma-delta digital RF modu- 40 lator for high data rate transmitters", published in IEEE Solid-State Circuits, vol. 42, no. 8, pp 1710-1722, Aug. 2007 [3], P. Eloranta, et al. "A multimode Transmitter in 0.13 m Using Direct-Digital RF Modulator", published in IEEE J. Solid-State Circuits, vol. 42, no. 12, pp 2774-2784, December 2007 [1]. Among them, the commercial single-chip GSM/EDGE transceiver in [1, 2] is unique in that it uses a simple array of unit-weighted transistor switches to control the output RF amplitude, which operates as near class-E power amplifier, instead of using a traditional current-source based DAC struc- 50 ture.

Concurrently to the digitization of RF transceivers, the RF performance requirements in wireless applications have been increasing, for example to support surface acoustic wave (SAW) filter removal, multi-mode operation, multi-band 55 operation, to meet coexistence requirements, etc. It is known that RF-DAC's need to achieve extremely-high resolution performance levels, which have so far been difficult to achieve in a practical, cost-effective manner. The traditional means of amplitude resolution in RF-DACs is limited due to 60 device mismatches, where the typical method of  $\Sigma\Delta$  dithering through noise shaping does not work well in SAW-less and multi-radio systems.

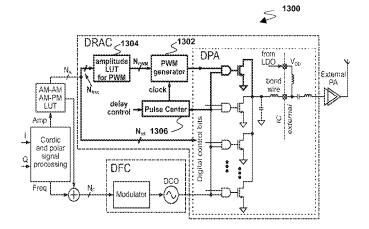

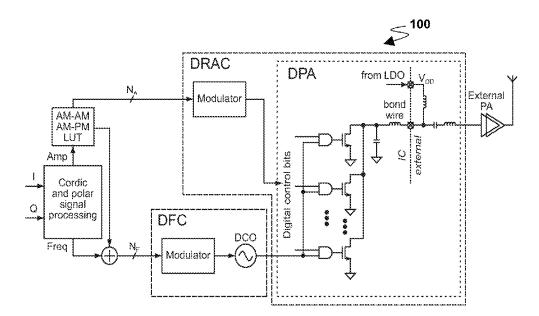

FIG. 1 illustrates the polar transmitter 100 introduced in [1, 2]. The I/Q baseband data is converted into digital amplitude 65 modulation (AM) and phase/frequency modulation (PM/FM) signals. The frequency signal is fed into the DCO-based  $N_{F}$ -

bit digital-to-frequency converter (DFC), which generates a digital phase-modulated RF carrier by means of an all-digital PLL (ADPLL). The amplitude signal drives the  $N_A$ -bit digital-to-RF-amplitude converter (DRAC), which includes a digitally-controlled power amplifier (DPA).

The DPA controls the envelope of the phase-modulated RF carrier, hence it is considered an RF-DAC. The DPA is different from the traditional RF-DACs in [3] or [4], because it does not use current sources. Therefore, the DPA is more compatible with low-voltage and low-cost digital CMOS processes than the traditional RF-DAC. Lack of current sources in the DPA results in somewhat compressed transfer function, but the look-up-table (LUT) for AM-AM and AM-PM predistortion in the amplitude signal path shown in FIG. 1 lin-

Referring now to FIG. 1, a known polar transmitter based on a DCO and DPA circuits from [2] is illustrated. For simplicity purposes, the all-digital PLL around the DCO is not shown. References [1, 2] have proved that the architecture in FIG. 1 is feasible for SoC meeting all GSM and EDGE specifications. However, the resolution of the amplitude modulation path is limited by lithography and RF mismatches (i.e., both amplitude and phase/delay) of the unit switching devices in the DPA, and, consequently, the polar transmitter has little margin in the far-out (i.e., the associated RX band) noise limit of the SAW-less operation for EDGE.

The amplitude resolution could be improved by  $\Sigma\Delta$  dithering of the unit transistor switches [1, 2]. However, the quantization noise is pushed to higher frequencies where emission requirements might sometimes be difficult to satisfy, especially when considering radio coexistence in a wireless connectivity (e.g., Bluetooth, WLAN) or in a multi-core RF-SoC environment.

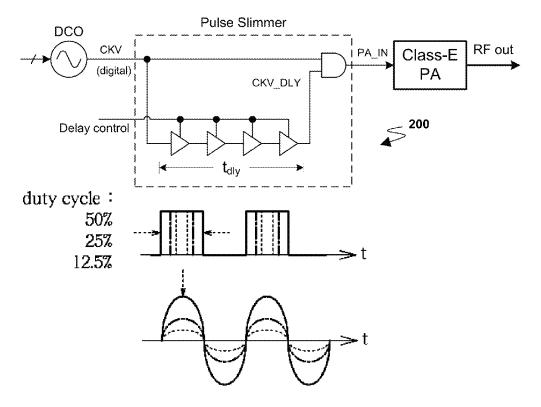

Referring now to FIG. **2**, a known concept **200** of achieving amplitude modulation (AM) through pulse width modulation (PWM) is illustrated. As shown, in the graphical waveform, the RF output amplitude is "proportional" to the duty cycle of a power amplifier input (PA\_IN) signal. A duty cycle of the AM signal is controlled through precise delay.

The output amplitude of a PWM signal at the frequency of interest, however, is incorrect if the pulsewidth is chosen in a straightforward way, such that the DC amplitude of the PWM signal is correct, as illustrated in S. E. Meninger and M. H. Perrott, titled "A fractional-N synthesizer architecture utilising a mismatch compensated PFD/DAC structure for reduced quantization-induced phase noise" published in IEEE Trans. Circuits Systems, vol. 50, issue 11, pp. 839-849, November 2003[7], which is incorporated herein by reference and S. E. Meninger and M. H. Perrott, titled "An RF Pulse Width Modulator for switch mode power amplification of varying envelope signals" published in Proc. Silicon Monolithic Integrated Circuits in RF System Top meeting, pp. 277-280, January 2007 [8], which is incorporated herein by reference. This is in contrast with the normal up-conversion operation of the DPA, which acts as a mixer. As a result, this inaccurate RF output level at the carrier frequency turns out to limit the resolution improvement.

Thus, a need exists for an improved amplitude resolution of an RF-DAC and method therefor.

#### SUMMARY

Accordingly, the invention seeks to mitigate, alleviate or eliminate one or more of the above mentioned disadvantages singly or in any combination. Aspects of the invention provide an integrated circuit controller, method of controlling an output of a digitally-controlled power amplifier (DPA), and a wireless communication unit as described in the appended claims. These and other aspects of the invention will be apparent from, and elucidated with reference to, the embodiments described hereinafter.

According to a first embodiment of the present invention, an integrated circuit is disclosed. The integrated circuit comprises a digitally-controlled power generation stage and a pulse width modulator (PWM) generator. The digitally-controlled power generation stage is arranged for converting an input signal to a radio frequency (RF) carrier, the digitallycontrolled power generation stage comprises a plurality of selectable switching devices capable of adjusting an envelope of the RF carrier. The PWM generator is arranged to generate a PWM control signal according to a fractional word and 15 operably coupleable to the plurality of selectable switching devices of the digitally-controlled power generation stage; wherein the PWM generator inputs the PWM control signal to a subset of the plurality of the selectable switching devices such that a PWM signal adjusts the envelope of the RF carrier 20 output from the digitally-controlled power generation stage.

According to a second embodiment of the present invention, a method of controlling an envelope of a radio frequency (RF) carrier output from a digitally-controlled power generation stage comprising a plurality of selectable switching <sup>25</sup> devices is disclosed. The method comprises: generating a pulse width modulator (PWM) control signal according to a fractional word; selecting a subset of the plurality of selectable switching devices to receive the PWM control signal; and, in response thereto generating a PWM signal to adjust <sup>30</sup> the envelope of the RF carrier output from the digitallycontrolled power generation stage.

According to a third embodiment of the present invention, a wireless communication unit is disclosed. The wireless communication unit comprises a digitally-controlled power 35 generation stage and a pulse width modulator (PWM) generator. The digitally-controlled power generation stage is arranged for converting an input signal to a radio frequency (RF) carrier, the digitally-controlled power generation stage comprises a plurality of selectable switching devices capable 40 of adjusting an envelope of the RF carrier. The PWM generator is arranged to generate a PWM control signal\_according to a fractional word and operably coupleable to the plurality of selectable switching devices of the digitally-controlled power generation stage; wherein the PWM generator inputs 45 the PWM control signal to a subset of the plurality of the selectable switching devices such that a PWM signal adjusts the envelope of the RF carrier output from the digitallycontrolled power generation stage.

These and other objectives of the present invention will no <sup>50</sup> doubt become obvious to those of ordinary skill in the art after reading the following detailed description of the preferred embodiment that is illustrated in the various figures and drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Further details, aspects and embodiments of the invention will be described, by way of example only, with reference to the drawings. Elements in the figures are illustrated for simplicity and clarity and have not necessarily been drawn to scale. Like reference numerals have been included in the respective drawings to ease understanding.

FIG. 1 illustrates a known polar transmitter based on a DCO and DPA circuits from [2].

FIG. **2** illustrates a known concept of achieving amplitude modulation through pulse width modulation.

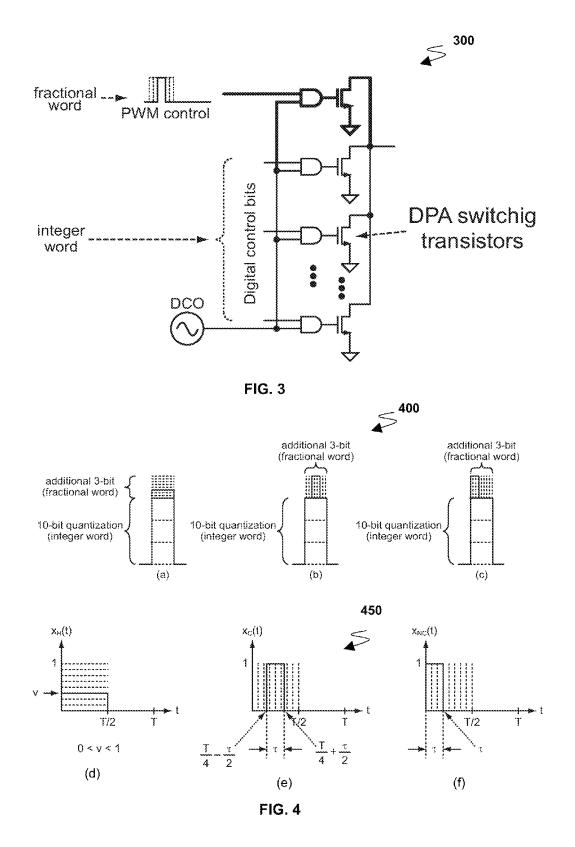

FIG. **3** illustrates an example of amplitude resolution improvement mechanism by incrementally adding a PWM driven transistor.

FIG. 4 illustrates an amplitude resolution improvement mechanism by first (a) horizontal slicing, (b) vertical slicing with centered PWM, (c) vertical slicing with non-centered PWM and secondly by (d) the fractional portion of horizontal slicing, (e) the fractional portion of vertical slicing with centered PWM, (f) the fractional portion of vertical slicing with non-centered PWM.

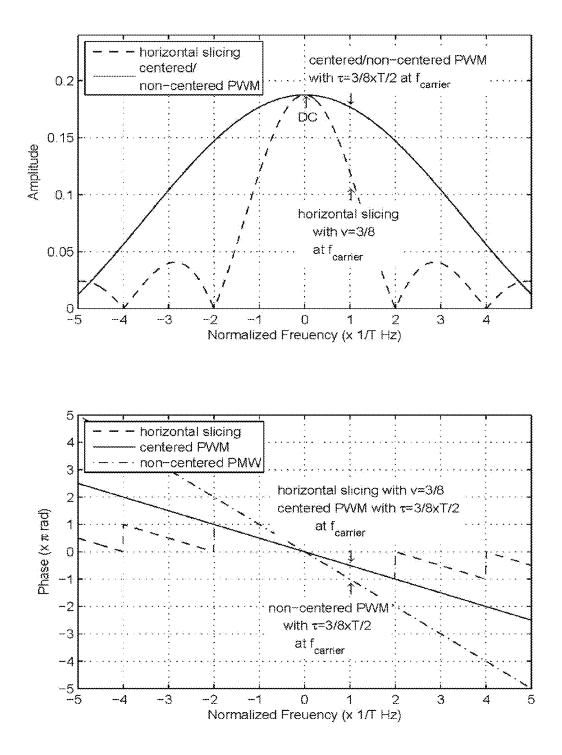

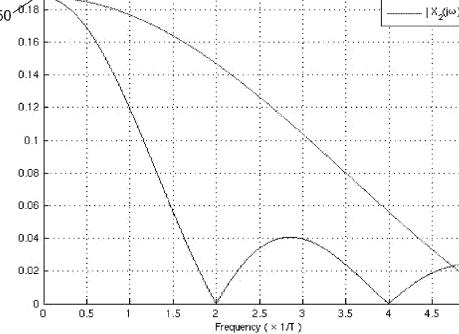

FIG. **5** illustrates a graphical example of frequency domain amplitude/phase comparison of horizontal slicing and vertical slicing (centered PWM and non-centered PWM) when

$$v = \frac{3}{8}$$

and  $\tau = \frac{3}{8} \times \frac{T}{2}$ .

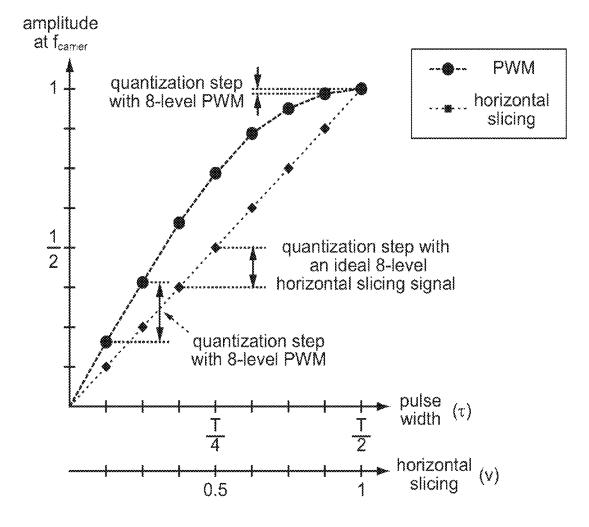

FIG. 6 illustrates a graphical example of amplitude quantization step at the carrier frequency of horizontal slicing signals and 8-level PWM signals from [8].

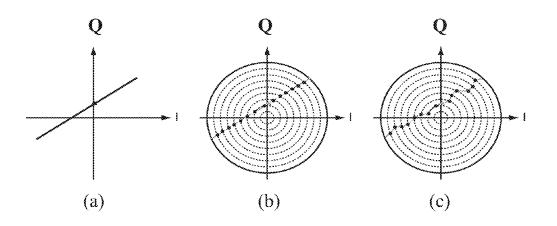

FIG. 7 illustrates a graphical example of symbol trajectories for an EDGE signal in I/Q plane, with (a) ideal trajectory (b) quantized trajectory without amplitude or phase error (c) quantized trajectory with phase error.

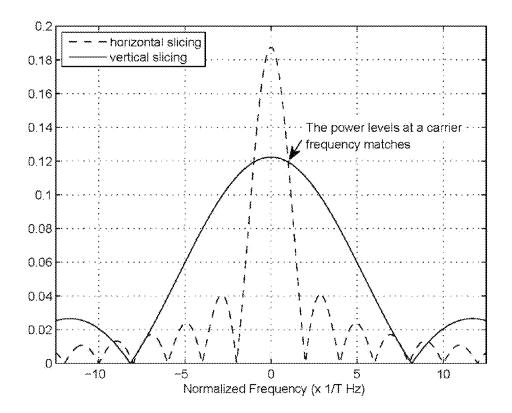

FIG.  $\mathbf{8}$  illustrates a graphical example of frequency domain amplitude comparison of horizontal slicing and centered PWM when

$v = \frac{3}{8}$

and  $\tau=0.122\times T$ .

65

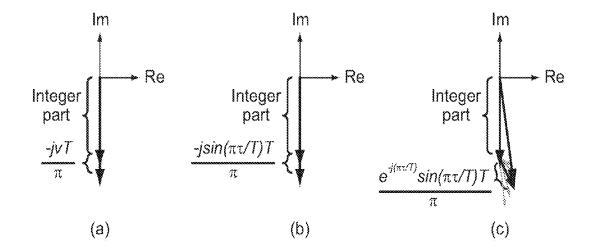

FIG. 9 illustrates a graphical example of (a) Vectors of an integer part of the amplitude signal and a horizontal slicing's fractional part (b) an integer part and a centered PWM's fractional part (c) an integer part and a non-centered PWM's fractional part.

FIG. **10** illustrates a graphical example of (a) Horizontal slicing (b) non-centered PWM in complex plane, where the entire complex plane is rotated 90° counter-clockwise.

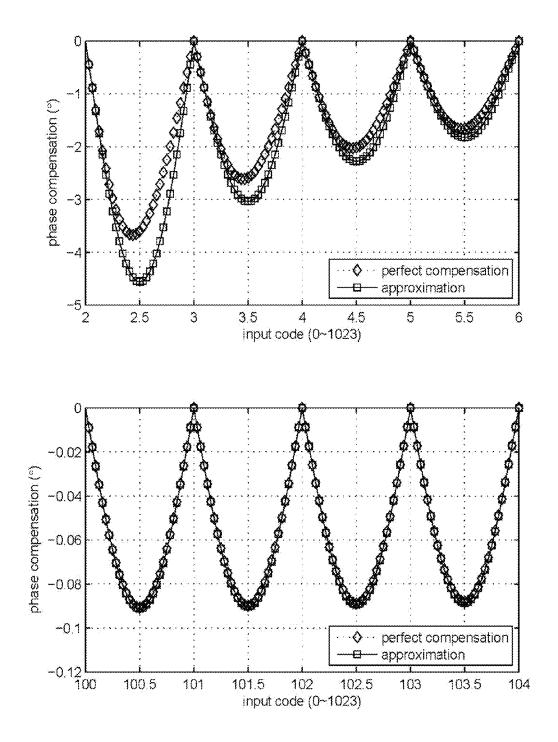

FIG. **11** illustrates a graphical example of a phase compensation comparison between equation (11) and equation (13) given below.

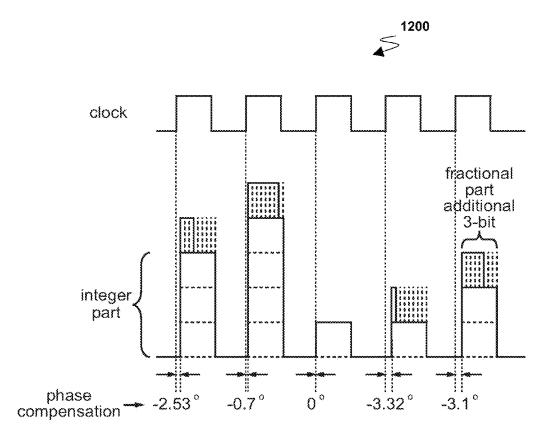

FIG. **12** illustrates a graphical example of timing diagrams of phase compensation for non-centered PWM.

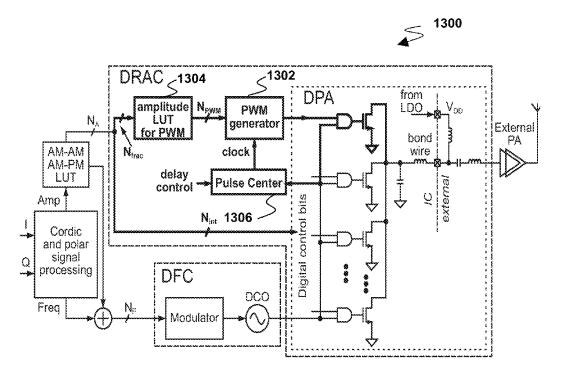

FIG. **13** illustrates an example of a polar transmitter with centered PWM in accordance with some example embodiments of the invention.

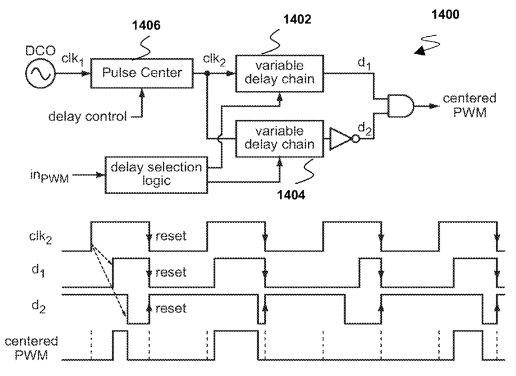

FIG. 14 illustrates an example of a conceptual block dia gram of a centered PWM generator and its timing diagram, in

accordance with some example embodiments of the invention.

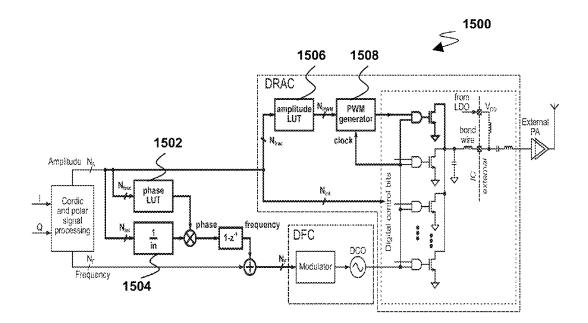

FIG. **15** illustrates an example of a polar transmitter with non-centered PWM, in accordance with some example embodiments of the invention.

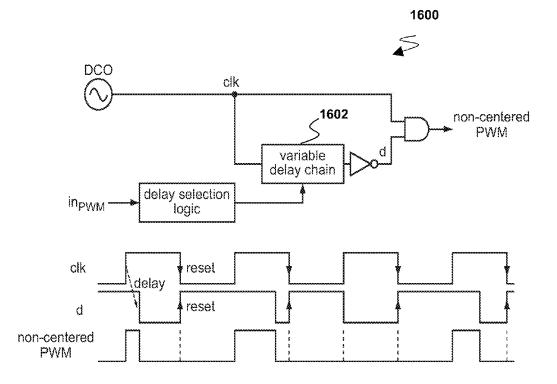

FIG. **16** illustrates an example of a conceptual block diagram of a non-centered PWM generator and its timing diagram, in accordance with some example embodiments of the invention.

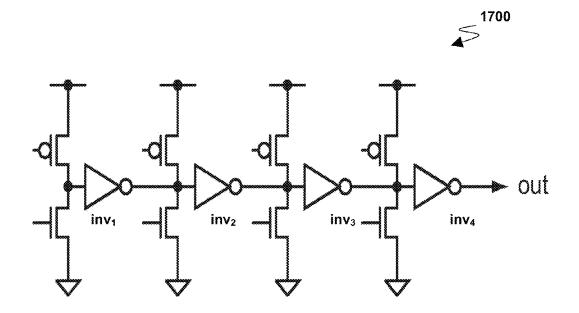

FIG. **17** illustrates an example of a conceptual delay chain for a PWM generator, in accordance with some example embodiments of the invention -5

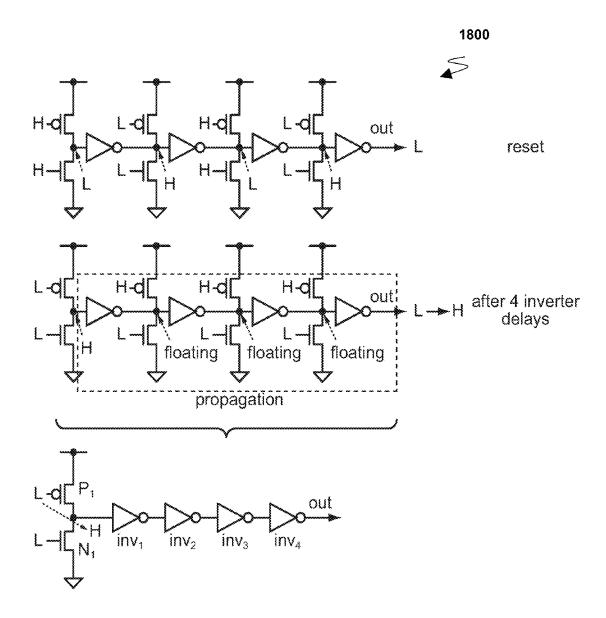

FIG. **18** illustrates an example of a 4-inverter delay circuit, in accordance with some example embodiments of the invention.

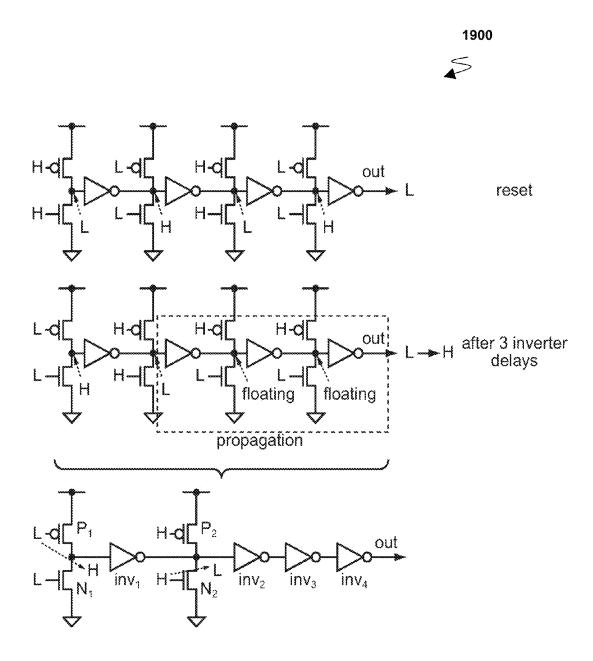

FIG. **19** illustrates an example of a 3-inverter delay circuit, in accordance with some example embodiments of the invention.

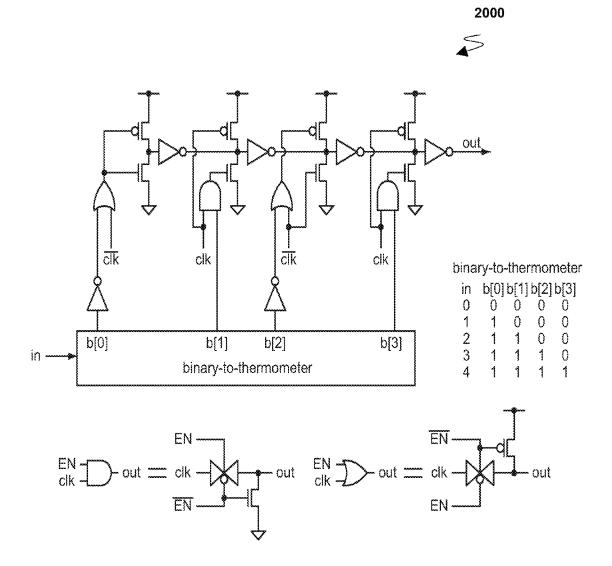

FIG. **20** illustrates an example of delay-chain circuits including control logic, in accordance with some example embodiments of the invention.

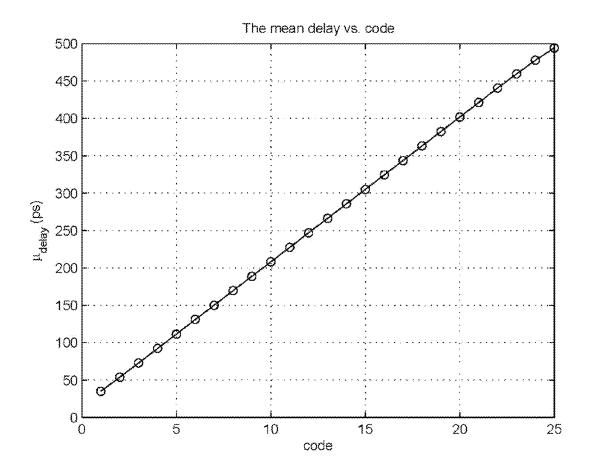

FIG. **21** illustrates a graphical example of a mismatchaveraged propagation (mean) delay versus input code of the circuit of FIG. **20**, in accordance with some example embodiments of the invention.

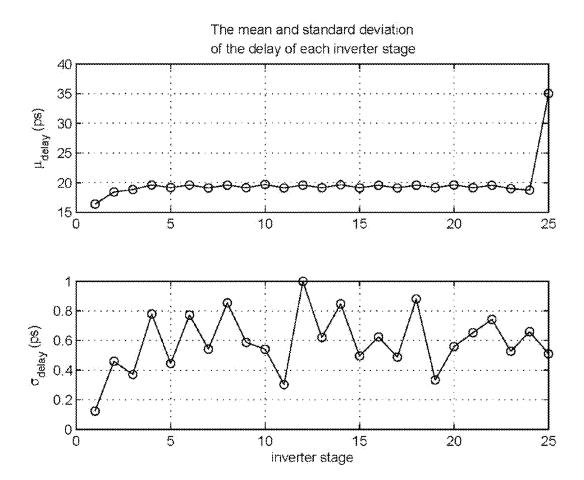

FIG. **22** illustrates an example of mean delays and standard <sup>15</sup> deviations of the inverter stage of FIG. **20**, in accordance with some example embodiments of the invention.

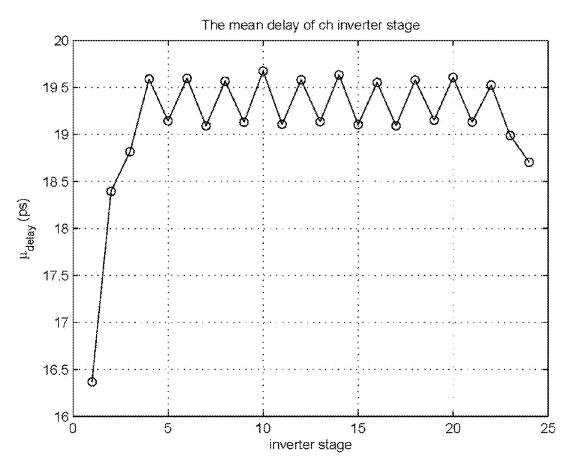

FIG. 23 illustrates an example of a mean delay of each inverter stage of the circuit of FIG. 20, in accordance with some example embodiments of the invention.

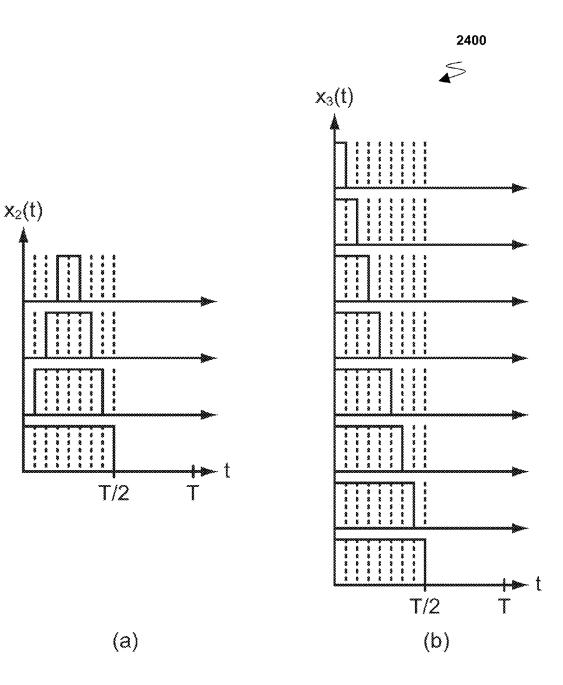

FIG. **24** illustrates a graphical example of a resolution comparison of centered and non-centered PWM generators with a unit delay of

$\frac{1}{8} \times \frac{T}{2}$

(a) centered PWM (b) non-centered PWM, in accordance with some example embodiments of the invention.

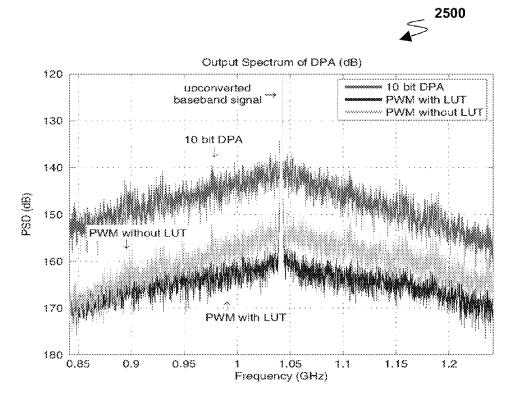

FIG. **25** illustrates an example of an output spectrum of a 10-bit DPA and a DPA with 12-level centered PWM signals with/without the amplitude predistortion LUT, in accordance with some example embodiments of the invention.

FIG. **26** illustrates an example of an output spectrum of a 10-bit DPA and a DPA with 12-level centered PWM signals with/without delay mismatch, in accordance with some example embodiments of the invention.

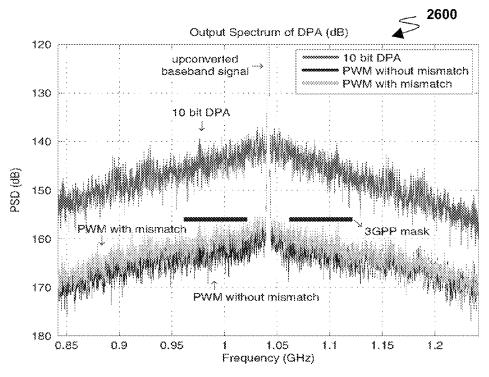

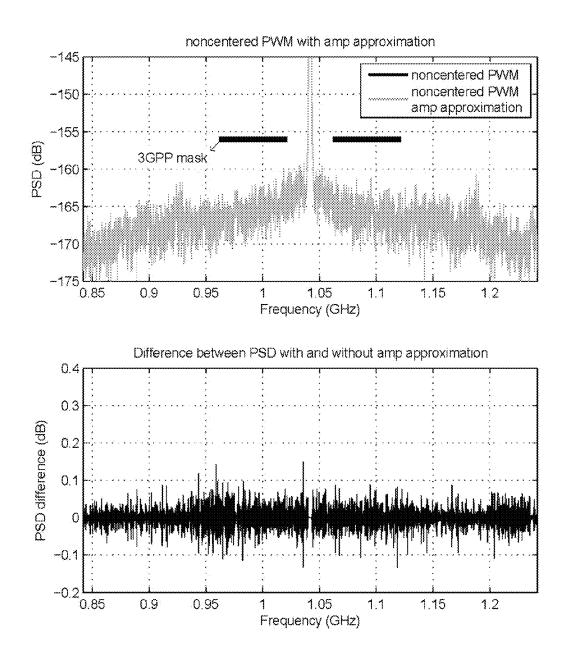

FIG. **27** illustrates an example of an output spectrum of a 40 centered PWM without position offset vs. centered PWM with 18-psec. position offset, where delay mismatch is not considered, in accordance with some example embodiments of the invention

FIG. **28** illustrates an example of an output spectrum of a 45 10-bit DPA and a DPA employing non-centered PWM signals with/without phase compensation, in accordance with some example embodiments of the invention.

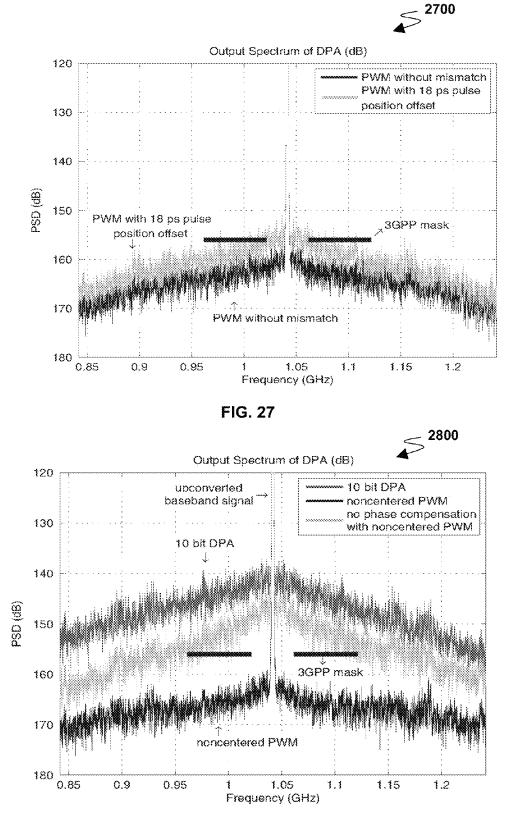

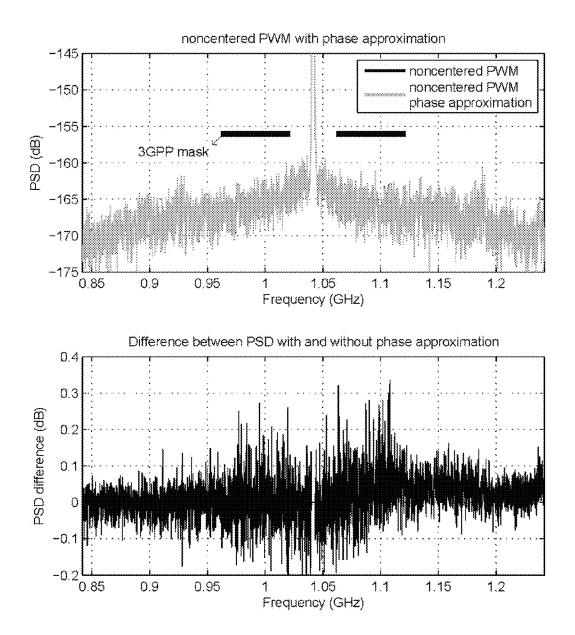

FIG. **29** illustrates an example of an output spectrum of a DPA employing non-centered PWM signals with reduced 50 size of an amplitude predistortion LUT by approximation, in accordance with some example embodiments of the invention

FIG. **30** illustrates an example of an output spectrum of a DPA employing non-centered PWM signals with reduced size of a phase predistortion LUT by approximation, in accor-55 dance with some example embodiments of the invention

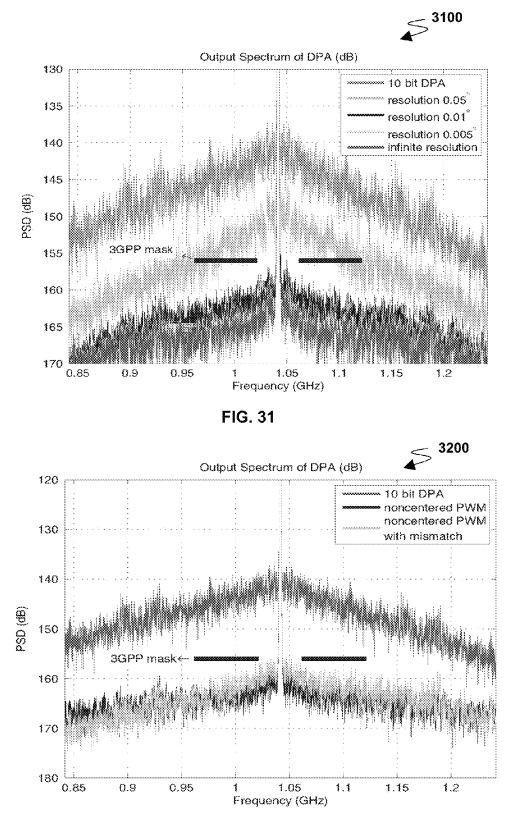

FIG. **31** illustrates an example of an output spectrum of a DPA employing non-centered PWM signals with different resolutions of a phase path, in accordance with some example embodiments of the invention.

FIG. **32** illustrates an example of an output spectrum of a DPA employing non-centered PWM signals with delay mismatch, in accordance with some example embodiments of the invention.

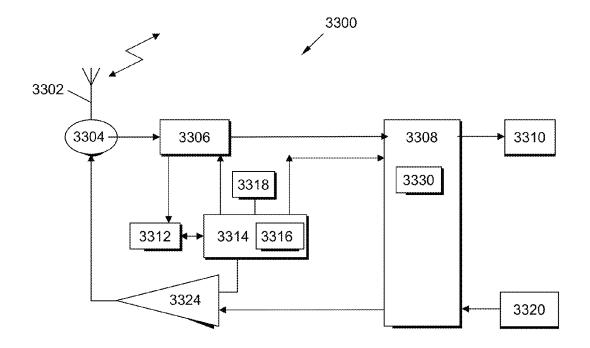

FIG. **33** illustrates an example of a wireless communication unit adapted to employ example embodiments of the invention.

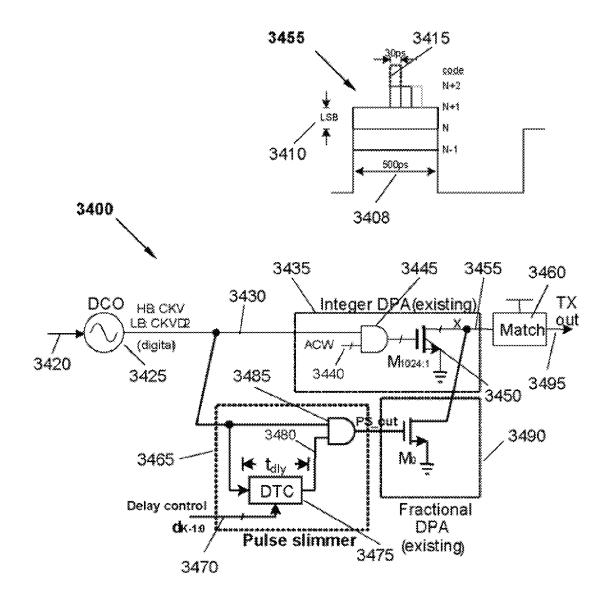

FIG. **34** illustrates an example of a RF-DAC employing PWM according to example embodiments of the invention.

FIG. **35** illustrates timing waveforms of the example RF-DAC employing PWM of FIG. **34** according to example embodiments of the invention.

FIG. **36** illustrates an example of a delay cell design, adapted to employ example embodiments of the invention.

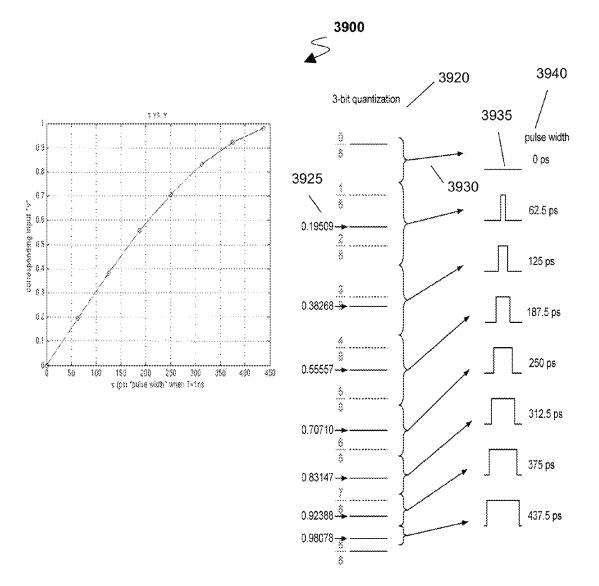

FIG. **37** illustrates a first bit-quantization example of the example RF-DAC employing PWM of FIG. **34** according to example embodiments of the invention.

FIG. **38** illustrates graphically a comparison of the two quantization methods to achieve the 3-bit quantization in the bit-quantization example employing PWM of FIG. **34** and FIG. **37** according to example embodiments of the invention.

FIG. **39** graphically a bit-quantization example using digital pre-distortion for a PWM pulse width of FIG. **34** according

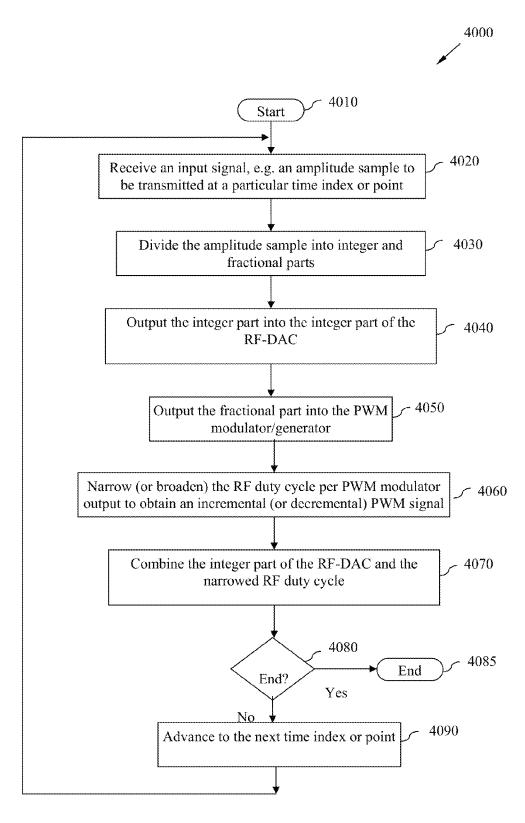

to example embodiments of the invention. FIG. **40** illustrates a flowchart of an operation of a RF-DAC employing iPWM according to example embodiments of the <sup>20</sup> invention.

#### DETAILED DESCRIPTION

Certain terms are used throughout the description and following claims to refer to particular components. As one skilled in the art will appreciate, electronic equipment manufacturers may refer to a component by different names. This document does not intend to distinguish between components that differ in name but not function. In the following description and in the claims, the terms "include" and "comprise" are used in an open-ended fashion, and thus should be interpreted to mean "include, but not limited to . . . ". Also, the term "couple" is intended to mean either an indirect or direct electrical connection. Accordingly, if one device is coupled to another device, that connection may be through a direct electrical connection, or through an indirect electrical connection via other devices and connections.

Examples of the invention will be described in terms of an integrated circuit (IC) comprising a radio-frequency digitalto-amplitude converter (RF-DAC) employing pulse width modulation (PWM). In examples of the invention, PWM is applied in an incremental fashion. Thus, hereinafter the term incremental PWM (iPWM) may be used to encompass and adjustment to (e.g. increment or decrement) a PWM signal. An RF-DAC is based on a concept of a digitally-controlled power amplifier (DPA). In general, a RF-DAC comprises a number of components, one of which is a power generation stage. Hereinafter, such a power generation stage will be described in the context of a DPA, as this term is widely used in the literature. Notwithstanding the above, in some instances, as these two terms RF-DAC and DPA are closely related, inasmuch as the DPA in some examples may equate to the RF-DAC with other components being provided external to an RF-DAC IC, the two terms may be used henceforth interchangeably. For completeness, it is noted that the term 'DPA' is somewhat of a misnomer, since the DPA input is not an analog RF signal and thus the notion of a 'gain' is incorrect here. Notwithstanding the aforementioned clarification of terms, it will be appreciated by a skilled artisan that the 60 inventive concept herein described may be embodied in any type of RF-DAC design.

Example embodiments of the invention focus on timedomain resolution of a digital signal edge transition, rather than the typical voltage resolution of analog signals, to improve the resolution of RF-DAC performance. Such an approach is particularly beneficial when using a highlyscaled CMOS technology. Examples of the invention will

55

also be described in terms of a digitally controlled power amplifier (DPA) that is used as an RF-DAC and arranged to convert a digital word into amplitude of an RF carrier. In this manner, examples of the invention may benefit from surface acoustic wave (SAW)-less implementations (e.g. designs without a requirement of a transmit bandpass filter connected to the RF output pin). Examples of the invention will also be described in terms of 'EDGE' (sometimes referred to as 2.5G) operation, standardised by the third generation partnership project (3GPPTM), which requires 13 bits of amplitude modu- 10 lation (AM) resolution for flat Q-noise to meet the EDGE wideband noise specification. Using the known technique of applying voltage resolution of analog signals to improve the resolution of RF-DAC performance has been found to be difficult to achieve an AM resolution of >10 bits by means of 15 device matching alone.

Example embodiments of the invention are described to help mitigate the far-out noise issue and make the digitallyintensive polar architecture of FIG. 1 more attractive to multicore RF integration, as well as to meet advanced modulation 20 standards. Example embodiments of the invention propose an RF-DAC structure in which significant resolution improvement is achieved by means of incremental pulse width modulation (PWM). PWM is a time-domain operation since the signal is carried in width or duration of a pulse, which is 25 time-domain information. In modern CMOS technology, time-domain processing can achieve higher resolution than voltage/current-domain processing because the switching time improves by device scaling, as described in R. B. Staszewski's Ph.D. thesis from Univ. of Texas, Dallas, USA "Digital deep-submicron CMOS frequency synthesis for RF wireless applications" [5], which is incorporated herein by reference. Although the novel and inventive amplitude resolution improvement is verified with a digital polar transmitter, in example embodiments of the invention, it may be also 35 applied to digitally-intensive I/Q architecture.

In example embodiments of the invention, the PWM may be categorized into centered PWM and non-centered PWM depending on the relative pulse position. The amplitude resolution improvement with centered PWM is presented in [6], 40 which is incorporated herein by reference. Example embodiments of the invention may extend the PWM scheme with non-centered PWM, and compare it with the centered PWM scheme in the context of implementation and performance.

Example embodiments of the invention discuss the details 45 of the PWM scheme to improve the amplitude resolution of the DPA. It will be shown that both centered and non-centered PWM create an incorrect RF signal when the pulse width is chosen in a straightforward way. Predistortion of PWM signals to generate a correct RF signal is then presented. LUT 50 size reduction technique for the non-centered PWM scheme will then follow. Different polar transmitter architectures for centered PWM and non-centered PWM are described, and behavioural simulation results of each PWM scheme are presented to show the benefits of the described methods.

Example embodiments of the invention describe a DPA that is augmented by at least one additional unit switching device that is driven by a PWM control signal, such that a PWM generator inputs the PWM control signal to a subset of a plurality of selectable switching devices such that a PWM 60 signal adjusts the envelope RF carrier output from the DPA, as shown in FIG. 3. In this context, the term 'adjusts' encompasses adding, substracting, combining, incrementing, decrementing or any other manner to modify the envelope RF carrier output from the DPA with a PWM control signal. However, in some examples, the amplitude resolution of the DPA improves by turning on the added switching device for

8

only a short time interval, for example within the positive half-cycle of the RF period. The RF output amplitude will be controlled by the time interval, and the resolution may be determined by the time precision of the turning-on signal.

Referring now to FIG. 3, an amplitude resolution improvement circuit 300, adding a PWM driven transistor, is illustrated. The amplitude resolution of the DPA in FIG. 3 is now limited by the time resolution of the PWM. In modern CMOS processes, the switching time gets typically improved by  $0.7 \times$ per technology scaling node; hence, achieving higher resolution in the time-domain is easier than in the voltage/currentdomain. In a 65 nm CMOS process, a minimum time resolution of 20 psec is easy to guarantee over process, temperature, and voltage variations.

The switching devices in the original system are controlled by an integer word of the digital amplitude signal. In order to increase the amplitude resolution of the original DPA, a fractional word of the amplitude controls the extra switching device in FIG. 3. Thus, the maximum error that the additional device can cause is less than the quantization noise of the original system. As a result, the added noise or jitter on the PWM signal does not affect the overall performance.

Referring now to FIG. 4, a graphical example of amplitude resolution improvement by (a) horizontal slicing, (b) vertical slicing with centered PWM, (c) vertical slicing with noncentered PWM is illustrated. To explain this issue, FIG. 4 first illustrates three different quantization methods 400 for adding an extra 3-bit resolution in either a voltage or current signal. For the DPA, the vertical axis in FIG. 4 represents the current or the conductance of the switching transistors, which is directly proportional to the output envelope, and its original resolution is 10 bits in the system of FIG. 1. FIG. 4-(a) shows horizontal slicing of a signal, which is a conventional quantization method for a DAC. Both FIG. 4-(b) and FIG. 4-(c)show vertical slicing of a signal where the output amplitude is controlled by the time interval of the vertically sliced signal. Note that the pulse in FIG. 4-(b) is located at the center, whereas that in FIG. 4(c) is aligned at t=0. This quantization method is PWM whose pulsewidth has a limited number of quantized pulsewidths. Depending on the position of the additive pulse, the vertical slicing method could be categorized as centered PWM and non-centered PWM, as shown in FIG. **4**-(*b*) and FIG. **4**-(*c*).

For the horizontal slicing scheme, the resolution is set by available area and power of switching transistors along with device mismatch, which limits the minimum device size. In contrast, the resolution of the vertical slicing scheme is set by the time-resolution. Accordingly, the vertical slicing can achieve higher resolution than the horizontal slicing with the same minimum device size if the time-resolution is finer. In modern nanometer-scale CMOS technology, the time-resolution is getting better, thus employing PWM seems a better choice to improve the amplitude resolution of a DPA.

Referring now to the second portion 450 of FIG. 4, an amplitude resolution improvement mechanism by (d) the fractional portion of horizontal slicing, (e) the fractional portion of vertical slicing with centered PWM, (f) the fractional portion of vertical slicing with non-centered PWM is illustrated. The second portion 450 of FIG. 4 illustrates only the first fractional portions from FIG. 4, where T is the time period of an RF carrier signal, v is an voltage/current level generated by the unit switching device using horizontal slicing, and  $\tau$  is a pulsewidth for vertical slicing. Note that the amplitude switches are only turned on during half the DCO period.

$\frac{T}{2}$ .

The full size of the voltage/current level generated by the unit switching device is normalized to '1'. In this example, the fractional word adds an extra 3-bit resolution with 8 extra amplitude levels. The pulse position of the PWM signal could be at the center of the first half cycle of the carrier signal <sup>10</sup> (centered PWM), or it could be aligned with the main switching waveform (non-centered PWM).

Intuitively, all the signals from FIG. 4-(d), (e), (f) are the same in terms of power because the total area of the signals <sup>15</sup> are the same. However, as pointed out in [7], which is incorporated herein by reference, they are equivalent only at DC. The Fourier transforms of the horizontal and vertical slicing signals are

$$\begin{split} X_H(j\omega) &= \int_0^{\frac{T}{2}} v \cdot e^{-j\omega t} dt = v \cdot \frac{2e^{-j\frac{\omega T}{4}} \cdot \sin\left(\frac{\omega T}{4}\right)}{\omega} \\ X_C(j\omega) &= \int_{\frac{T}{4}-\frac{\tau}{2}}^{\frac{T}{4}+\frac{\tau}{2}} e^{-j\omega t} dt = \frac{2e^{-j\frac{\omega T}{4}} \cdot \sin\left(\frac{\omega \tau}{2}\right)}{\omega} \\ X_{NC}(j\omega) &= \int_0^{\tau} 1 \cdot e^{-j\omega t} dt = \frac{2e^{-j\frac{\omega \tau}{2}} \sin\left(\frac{\omega \tau}{2}\right)}{\omega} \end{split}$$

where  $X_{H}(j\omega)$ ,  $X_{C}(j\omega)$ , and  $X_{NC}(j\omega)$  are the Fourier transforms of the horizontal slicing, the centered PWM, and the <sup>35</sup> non-centered PWM signals, respectively. In the examples of FIG. **4**, v is <sup>3</sup>/<sub>8</sub>, and  $\tau$  is

$$v$$

is  $\frac{3}{8}$ , and  $\tau$  is  $\frac{3}{8} \times \frac{T}{2}$ .

FIG. **5** illustrates the amplitudes and the phases of the Fourier transforms of each case, and it clearly shows that horizontal and vertical slicing is not the same at the carrier frequency, which is

$$\frac{1}{T}$$

Hz. First of all, the amplitude of the Fourier transform of horizontal slicing is different from that of vertical slicing. <sup>55</sup> Second of all, the phase of vertical slicing with non-centered PWM is different from that of horizontal slicing although the phase of centered PWM is the same as that of horizontal slicing. An RF-DAC is intended to generate a signal at a carrier frequency corresponding to an input digital code. <sup>60</sup> Therefore, the vertical slicing signal in FIG. **5** creates an incorrect RF signal even though it creates an accurate DC signal.

An inaccurate RF signal from an RF-DAC leads to higher <sub>65</sub> quantization noise. The Fourier transforms at a carrier frequency

10

$$\left(\omega = \frac{2\pi}{T}\right)$$

should be examined for quantization noise analysis for an RF-DAC, and they are

$$X_H(j\omega)|_{\omega=\frac{2\pi}{T}} = \frac{-jvT}{\pi}$$

(1)

$$(j\omega)|_{\omega^{2\pi}} = \frac{-j\sin(\frac{\pi\tau}{T})T}{\pi}$$

<sup>(2)</sup>

$$X_{NC}(j\omega)|_{\omega=2\pi} = (e^{-j(\pi T/T)} * \sin(\omega T/2) * T)/\pi$$

(3)

FIG. 6 depicts the amplitudes at the carrier frequency of the 8-level horizontal and vertical slicing signals, which are

derived in (1) and (2) as a function of pulsewidth and horizontal slicing level. Note that the amplitudes of (2) and (3) are the same. The maximum amplitude at the carrier frequency is normalized to 1 for simple quantization error estimation, and Table 1 shows the RF amplitude for each input code and the

corresponding quantization error. In Table 1, the range of the quantization error of vertical slicing is much larger than

$$\frac{1}{16} = 0.0625.$$

30

45

50

It means that the quantization noise by vertical slicing is bigger than that of horizontal slicing. The quantization noise power can be estimated by a probability density function assuming the probability of error is uniformly distributed. The calculated noise power shows that horizontal slicing achieves 3-bit resolution while vertical slicing achieves only 0.9-bit resolution. Therefore, resolution improvement by PWM is severely impaired if the pulsewidth is chosen in such a way that the DC amplitude of a vertical slicing signal is matched with that of a horizontal slicing signal, as shown in FIG. **6** and Table 1.

TABLE 1

| Quantization error by horizontal and centered PWM |                                 |                          |                       |                          |                       |  |

|---------------------------------------------------|---------------------------------|--------------------------|-----------------------|--------------------------|-----------------------|--|

|                                                   |                                 | horizo                   | ontal slicing         | centered PWM             |                       |  |

| original<br>input                                 | pulse<br>width                  | amp<br>at f <sub>C</sub> | quantization<br>error | amp<br>at f <sub>C</sub> | quantization<br>error |  |

| 0-1/16                                            | 0                               | 0                        | -1/16-0               | 0                        | -1/16-0               |  |

| 1/16-3/16                                         | $\frac{1}{8}\cdot\frac{T}{2}$   | 1/8                      | -1/16-1/16            | 0.194                    | 0.132<br>0.007        |  |

| 3/16-5/16                                         | $\frac{2}{8} \cdot \frac{T}{2}$ | 2/8                      | -1/16-1/16            | 0.383                    | 0.195<br>0.070        |  |

| 5/16-7/16                                         | $\frac{3}{8} \cdot \frac{T}{2}$ | 3/8                      | -1/16-1/16            | 0.556                    | 0.243<br>0.118        |  |

| 7⁄16-9⁄16                                         | $\frac{4}{8} \cdot \frac{T}{2}$ | 4/8                      | -1/16-1/16            | 0.707                    | 0.270<br>0.145        |  |

| 9/16-11/16                                        | $\frac{5}{8} \cdot \frac{T}{2}$ | 5/8                      | -1/16-1/16            | 0.832                    | 0.269<br>0.144        |  |

|                                                               |                               |                                        | 1-continued           |                          |                       |   |

|---------------------------------------------------------------|-------------------------------|----------------------------------------|-----------------------|--------------------------|-----------------------|---|

| Qua                                                           | intization e                  | n error by horizontal and centered PWM |                       |                          |                       | _ |

| original<br>input                                             | pulse<br>width                | amp<br>at f <sub>C</sub>               | quantization<br>error | amp<br>at f <sub>C</sub> | quantization<br>error |   |

| 11/16-13/16                                                   | $\frac{6}{8}\cdot\frac{T}{2}$ | 6⁄8                                    | -1/16-1/16            | 0.924                    | 0.236-0.111           | 1 |

| <sup>13</sup> / <sub>16</sub> - <sup>15</sup> / <sub>16</sub> | $\frac{7}{8}\cdot\frac{T}{2}$ | 7/8                                    | -1/16-1/16            | 0.981                    | 0.168-0.043           | 1 |

| 15/16-16/16                                                   | $\frac{8}{8}\cdot\frac{T}{2}$ | 8/8                                    | -1/16-0               | 1                        | -1/16-0               | 1 |

Vertical slicing with non-centered PWM distorts the signal even further due to it phase discrepancy. The phase of the Fourier transforms in (1) and (2) is

| π              |  |

|----------------|--|

| $\overline{2}$ |  |

regardless of v or  $\tau$ , but the phase in (3) is dependent on  $\tau$ . Accordingly, the phase of the Fourier transforms of the horizontal slicing signals and the non-centered PWM signals are different unless  $\tau$  is

$$\frac{T}{2}$$

.

Thus, the phase of non-centered PWM should be compen-<sup>35</sup> sated for the correct symbol representation.

The importance of phase compensation is presented in FIG. 7. It illustrates the trajectories of an example of EDGE symbols in an I/Q plane with and without phase error. FIG. 7-(*a*) shows the ideal symbol trajectory without any ampli- 40 tude/phase quantization. FIG. 7-(*b*) shows the symbol trajectory with amplitude quantization. There is no phase error in this case so that its spectrum will show only the noise due to the amplitude quantization error. Horizontal slicing and centered PWM signals will show this symbol trajectory. FIG. 45 7-(*c*) shows the trajectory with amplitude quantization and phase error. Even though it has the same amplitude quantization as 7-(*b*), the phase error results in uneven symbol trajectory, which will cause more noise in the spectrum. Predistortion of PWM Signals 50

Amplitude distortion of PWM exists for both centered and non-centered PWM. In contrast, phase distortion is caused by only non-centered PWM. We will first discuss how to avoid or reduce amplitude distortion of centered PWM, which was briefly introduced in [6], and then discuss phase and ampli-55 tude distortion of non-centered PWM.

Predistortion of PWM Signal for Centered PWM One solution to the amplitude discrepancy between horizontal slicing and centered PWM is choosing the pulsewidth for the vertical slicing such that its amplitude at the carrier frequency is the same as that of corresponding horizontal slicing.

$$X_H(j\omega)\Big|_{\omega=rac{2\pi}{T}} = X_C(j\omega)\Big|_{\omega=rac{2\pi}{T}}$$

$$\frac{-jvT}{\pi} = \frac{-j\sin(\frac{\pi t}{T})T}{\pi}$$

$$v = \sin(\frac{\pi \tau}{T})$$

Equation (4) shows how to choose the pulsewidth for the centered PWM signal. A centered PWM signal whose pulsewidth satisfies (4) has the same amplitude as the corresponding horizontal slicing signal at the carrier frequency. Note that the centered PWM signal has the same phase as that of the horizontal slicing signal. Thus, phase distortion is not a concern for a centered PWM signal.

TABLE 2

|    |                       | e same amplitude at a carrier<br>ding horizontal slicing signals |  |

|----|-----------------------|------------------------------------------------------------------|--|

| 20 | horizontal<br>slicing | pulsewidth                                                       |  |

|    | 0                     | 0                                                                |  |

|    | 1/8                   | 0.0399 × T                                                       |  |

| 25 | 2/8                   | $0.0804 \times T$                                                |  |

| 25 | 3/8                   | 0.122 × T                                                        |  |

|    | 4/8                   | 0.167 × T                                                        |  |

|    | 5/8                   | 0.215 × T                                                        |  |

|    | 6/8                   | 0.270 × T                                                        |  |

|    | 7/8                   | 0.339 × T                                                        |  |

FIG. 8 depicts an example of the amplitude of the Fourier transform of the centered PWM signal satisfying (4). In FIG. 8, it is clear that the amplitude of the centered PWM signal at the carrier frequency is the same as that of the horizontal slicing signal. Table 2 shows an example of the pulsewidths, for which the amplitude and the phase at the carrier frequency is the same as those of the corresponding horizontal slicing signals. The amplitude resolution of the centered PWM signals employing the pulsewidths shown in Table 2 is also the same as that of horizontal slicing signals. Unfortunately, the pulsewidths shown in Table 2 are very challenging to generate without an accurate delay controller, such as a high precision DLL or a fine-resolution delay line. Therefore, such PWM generation is impractical.

TABLE 3

| 50 |                    |                                           | multiples of $\frac{T}{16}$ , and tal slicing signals | l the                                     |

|----|--------------------|-------------------------------------------|-------------------------------------------------------|-------------------------------------------|

|    | horizontal slicing | pulsewidth                                | horizontal slicing                                    | pulsewidth                                |

| 55 | 0                  | 0                                         | 0.707                                                 | $\frac{4}{8} \times \frac{\mathrm{T}}{2}$ |

|    | 0.194              | $\frac{1}{8} \times \frac{T}{2}$          | 0.831                                                 | $\frac{5}{8} \times \frac{\mathrm{T}}{2}$ |

| 60 | 0.383              | $\frac{2}{8} \times \frac{\mathrm{T}}{2}$ | 0.924                                                 | $\frac{6}{8} \times \frac{T}{2}$          |

|    | 0.556              | $\frac{3}{8} \times \frac{\mathrm{T}}{2}$ | 0.981                                                 | $\frac{7}{8} \times \frac{\mathrm{T}}{2}$ |

(4) 65 A PWM signal is easier to generate when its pulsewidth is integer multiples of a certain stable delay. Table 3 shows an example in which the pulsewidths are integer multiples of

| T  |   |  |  |

|----|---|--|--|

| 16 | • |  |  |

It also presents the corresponding horizontal slicing signals that satisfy (4). A simple delay chain can generate those pulsewidths shown in Table 3; hence, it is a better implementation choice. However, the relationship between the desired horizontal slicing signals and the pulsewidths shown in Table  $_{10}$ 3 is nonlinear. A predistortion digital LUT can be utilized to implement this mapping, where the contents of the predistortion LUT should be chosen such that the amplitude quantization error is minimized.

Table 4 presents an example of a predistortion digital LUT  $_{15}$ for mapping the input code to the appropriate pulsewidth of centered PWM. In the example of Table 4, the LUT maps the 5-bit input to 8-level pulsewidths. The LUT mapping linearizes the relationship between the input code and the output amplitude at the carrier frequency such that the amplitude  $_{20}$ quantization error is minimized. Note that the range of the quantization errors in Table 4 are sometimes larger than the maximum quantization error of the ideal 8-level signal, which is ±

$$\pm \frac{1}{16} = \pm 0.0625.$$

FIG. 6 explains the reason of the larger quantization noise of 30 the LUT in Table 4 more clearly. The quantization step is larger than that of ideal 8-level horizontal slicing when the pulsewidths are relatively short, as shown in FIG. 6. Therefore, the quantization error using the predistortion LUT and 8-level centered PWM will be larger than that of the ideal 35 3-bit horizontal slicing. The quantization noise power of the centered PWM employing the LUT in Table 4 can be also calculated by probability density functions, and the calculated amplitude resolution at the carrier frequency is 2.6 bits.

As we have seen in Table 2 and Table 3, there are two 40 options to linearize the RF power of a PWM signal:mapping uniform data input to non-uniform pulsewidths (Table 2), and mapping non-uniform data input to uniform pulsewidths (Table 3). Apparently, uniform-to-non-uniform mapping needs no sacrifice for achieving 3-bit resolution, while non- 45 uniform-to-uniform mapping shows the resolution degradation by 0.4 bits. However, the pulsewidths in Table 3 are easy to generate using a simple delay chain. The predistortion LUT is also easy to implement in digital CMOS processes. Therefore, we propose to employ a predistortion LUT for centered 50 PWM, which helps to minimize the overall system complexity with slight degradation of amplitude resolution.

| IABLE 4 |

|---------|

|---------|

| original<br>input                  | LUT<br>input | pulsewidth<br>selected | $ \substack{ \text{amp} \\ \text{at } \mathbf{f}_C } $ | quantization<br>error |

|------------------------------------|--------------|------------------------|--------------------------------------------------------|-----------------------|

| 0-1/64                             | 0            | 0                      | 0                                                      | 0<br>0.0156           |

| <sup>1</sup> /64- <sup>3</sup> /64 | 1/32         | 0                      | 0                                                      | 0.0156<br>0.0469      |

| 3/64-5/64                          | 2/32         | 0                      | 0                                                      | 0.0469                |

| 14                |

|-------------------|

| TABLE 4-continued |

| TABLE 4-continued                    |                                                                        |                                 |                                                 |                       |  |  |

|--------------------------------------|------------------------------------------------------------------------|---------------------------------|-------------------------------------------------|-----------------------|--|--|

| Look-up-table                        | Look-up-table example with 5-bit input and 8-level centered PWM output |                                 |                                                 |                       |  |  |

| original<br>input                    | LUT<br>input                                                           | pulsewidth<br>selected          | $\substack{\text{amp}\\\text{at }\mathbf{f}_C}$ | quantization<br>error |  |  |

| 7/64-9/64                            | 4/32                                                                   | $\frac{1}{8} \cdot \frac{T}{2}$ | 0.194                                           | -0.0857<br>0.0545     |  |  |

| 9/64-11/64                           | 5/32                                                                   | $\frac{1}{8}\cdot\frac{T}{2}$   | 0.194                                           | -0.0545<br>-0.0232    |  |  |

| 11/64-13/64                          | 6/32                                                                   | $\frac{1}{8} \cdot \frac{T}{2}$ | 0.194                                           | -0.0232<br>0.0804     |  |  |

| 13/64-15/64                          | 7/32                                                                   | $\frac{1}{8} \cdot \frac{T}{2}$ | 0.194                                           | 0.00804<br>0.0393     |  |  |

| 15/64-17/64                          | 8/32                                                                   | $\frac{1}{8} \cdot \frac{T}{2}$ | 0.194                                           | 0.0393<br>0.0705      |  |  |

| 17/64-19/64                          | 9/32                                                                   | $\frac{1}{8}\cdot\frac{T}{2}$   | 0.194                                           | 0.0705<br>0.102       |  |  |

| 19/64-21/64                          | 10/32                                                                  | $\frac{2}{8}\cdot\frac{T}{2}$   | 0.383                                           | -0.0858<br>-0.0546    |  |  |

| 21/64-23/64                          | 11/32                                                                  | $\frac{2}{8} \cdot \frac{T}{2}$ | 0.383                                           | -0.0546<br>-0.0233    |  |  |

|                                      |                                                                        | <br><br>                        |                                                 |                       |  |  |

| 53/64-55/64                          | 27/32                                                                  | $\frac{5}{8}\cdot\frac{T}{2}$   | 0.831                                           | -0.00335<br>-0.0279   |  |  |

| <sup>55</sup> /64- <sup>57</sup> /64 | <sup>28</sup> / <sub>32</sub>                                          | $\frac{5}{8} \cdot \frac{T}{2}$ | 0.831                                           | 0.0279<br>0.0592      |  |  |

| 57/64-59/64                          | 29/32                                                                  | $\frac{6}{8}\cdot\frac{T}{2}$   | 0.924                                           | -0.00333<br>-0.00201  |  |  |

| 59/64-61/64                          | 30/32                                                                  | $\frac{6}{8} \cdot \frac{T}{2}$ | 0.924                                           | -0.00201<br>0.0292    |  |  |

| 61/64-63/64                          | 31/32                                                                  | $\frac{7}{8} \cdot \frac{T}{2}$ | 0.981                                           | -0.0277<br>0.0359     |  |  |

| 63/64-64/64                          | 31/32                                                                  | $\frac{7}{8} \cdot \frac{T}{2}$ | 0.981                                           | -0.0156<br>0          |  |  |

Predistortion of PWM Signals for Non-Centered PWM

In contrast to the centered PWM, phase compensation is required for non-centered PWM as the phase of the Fourier transforms of the horizontal slicing signals and the non-centered PWM signals are different. Therefore, the phase error 55 created by a non-centered PWM signal should be compensated. The novel and inventive PWM scheme is verified with a digital polar transmitter including a PLL, which can manipulate the phase of an RF signal. The PLL can compensate the phase error, but it requires an additional LUT for the phase signal path.

Not only the phase but also the amplitude of the Fourier transform of non-centered PWM is different from that of centered PWM. Equations (1), (2), and (3) are the Fourier <sup>65</sup> transforms of the fractional part of the amplitude signal only. The Fourier transforms of the complete signals including both the integer and the fractional portions are:

(5)

(7)

15

$$X_{H,total}(j\omega)\big|_{\omega=\frac{2\pi}{T}} = \frac{-jVT}{\pi} + \frac{-jvT}{\pi}$$

$$X_{C,total}(j\omega)\Big|_{\omega=\frac{2\pi}{T}} = \frac{-jVT}{\pi} + \frac{-j\sin\left(\frac{\pi\tau}{T}\right)T}{\pi}$$

(6)

$$X_{NC,total}(j\omega)|_{c=\frac{2\pi}{2}} = -jVT/\pi + (e^{-j(\pi T/T)} * \sin(\pi T/T) * T)/\pi$$

where:

$X_{H,total}(j\omega), X_{C,total}(j\omega)$ , and  $X_{NC,total}(j\omega)$  are the Fourier transforms of the horizontal slicing, the centered PWM, and the non-centered PWM signals, respectively, including both the integer and fractional part. V is the integer portion, which is generated by a DPA. In some example embodiments, as described herein, the DPA may encompass a subset of the full DPA (e.g. a subset of the full power generation stage). The phases of the integer part and the fractional part in equations (5) and (6) are the same. Therefore, if the fractional portion of a centered PWM signal in equation (6) is the same as that of the targeted horizontal slicing signal in equation (5), then the amplitudes of the complete signals are the same. In other words,  $\tau$  for centered PWM is only dependent on v not V. However, as shown in equation (7), the phase of the fractional part of a non-centered PWM signal is different from that of the integer part; hence, the amplitude of the final signal is a vector sum in complex plane. FIG. 9 illustrates the situation more clearly. The goal of choosing the appropriate pulsewidth  $\tau$  for centered and non-centered PWM is to make the total signal including the integer portion the same as the ideal horizontal slicing signal, which is depicted in FIG. 9-(a). For centered PWM, it is a simple task because the pulsewidth  $\tau$  is 35 determined by only v, and it is independent of the integer portion V. For non-centered PWM, however, the phase of the fractional portion is not the same as that of the integer portion; as a result, the amplitude of the total signal is a vector sum of the integer and the fractional parts, as shown in FIG. 9-(c).  $_{40}$ The vector sum is a function of the integer part as well as the pulsewidth  $\tau$ . Therefore, the amplitude predistortion LUT for non-centered PWM should take the integer part into consideration while the LUT for centered PWM only takes the fractional part as its input. In other words, the size of the 45 amplitude predistortion LUT for non-centered PWM should be bigger than the LUT for centered PWM.

As an example, the full-length size of the amplitude predistortion LUT for the non-centered PWM should be 32768 words (15-bit=10-bit+5-bit) if the integer word of the amplitude is 10 bits and the fractional word is 5 bits. However, the size of the amplitude predistortion LUT for centered PWM will be only 32 words (5-bit) because the LUT takes only the fractional part as an input. Accordingly, non-centered PWM requires much bigger amplitude predistortion LUT than centered PWM.

Nevertheless, under certain conditions, the size of the amplitude predistortion LUT for non-centered PWM can be significantly reduced by approximation. According to the 60 equation below, the phase of the integer part is always imaginary, and the phase of the fractional part has both real and imaginary parts that depend on  $\tau$ . Note that the real part comes only from the fractional word. The equation below can be separated into the real and imaginary part, and the real part 65 can be neglected if the integer portion, V, is much larger than the fractional portion, as follows.

(8)

$$X_{NC,total}(j\omega)|_{\omega=\frac{2\pi}{T}} = \frac{-jVT}{\pi} + \frac{e^{-j\frac{\pi\tau}{T}}\sin(\frac{\pi\tau}{T})T}{\pi} =$$

$$\frac{-jVT}{\pi} - \frac{j\sin(\frac{\pi\tau}{T})\sin(\frac{\pi\tau}{T})T}{\pi} + \frac{\cos(\frac{\pi\tau}{T})\sin(\frac{\pi\tau}{T})T}{\pi}$$

$$X_{NC,total}(j\omega)|_{\omega=\frac{2\pi}{T}} \approx \frac{-jVT}{\pi} - \frac{j\sin(\frac{\pi\tau}{T})\sin(\frac{\pi\tau}{T})T}{\pi}$$

$$ifV \gg \cos(\frac{\pi\tau}{T})\sin(\frac{\pi\tau}{T})$$

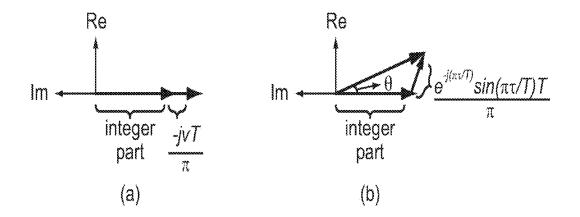

Equation (8) is valid if V is large enough. In FIG. 10, we can easily see that  $\theta$  will become very small as V, which represents the integer part of the baseband signal, increases such that the real part becomes negligible compared to the imaginary part. Therefore, equation (8) is a very good approximation for the large amplitude signals. For an EDGE signal, the amplitude is always larger than certain amplitude in order to keep its peak-to-minimum ratio of signal around 16.4 dB. V might be large enough to satisfy the condition for equation (8) if the baseband input signal is an EDGE signal. Validity of equation (8) for an EDGE signal is verified by simulations and the results will be presented later. If equation (8) is valid, the same size of the amplitude predistortion LUT as centered PWM can be employed for amplitude predistortion of noncentered PWM. The LUT should be realized based on the following equation:

$$\begin{aligned} X_H(j\omega)|_{\omega=\frac{2\pi}{T}} &= X_{NC}(j\omega)|_{\omega=\frac{2\pi}{T}} \\ &= \frac{-j v T}{\pi} = \frac{-j \sin\left(\frac{\pi \tau}{T}\right) \sin\left(\frac{\pi \tau}{T}\right) T}{\pi} \\ v &= \sin\left(\frac{\pi \tau}{T}\right) \sin\left(\frac{\pi \tau}{T}\right) \end{aligned}$$

(9)

Furthermore, FIG. 9-(c) indicates that not only an amplitude predistortion LUT, but also a phase compensation LUT, should take the integer part of the amplitude into account because the phase of the non-centered PWM signal depends on the integer word as well as  $\tau$ . As a result, the size of the phase predistortion LUT will be huge. However, some approximation technique can help to reduce its size, too.

FIG. 10 shows a comparison 1000 of an ideal horizontal slicing signal and a non-centered PWM counterpart 1000. Note that the entire complex plane is rotated by 90° counterclockwise for easy tan<sup>-1</sup> approximation. The amount of phase  $_{55}$  distortion by non-centered PWM is  $\theta$ , which is

$$\Theta = \tan^{-1} \left( \frac{\frac{\cos\left(\frac{\pi\tau}{T}\right)\sin\left(\frac{\pi\tau}{T}\right)T}{\frac{\pi}{T}}}{\frac{VT}{\pi} + \frac{\sin\left(\frac{\pi\tau}{T}\right)\sin\left(\frac{\pi\tau}{T}\right)T}{\pi}} \right)$$

(1)

$$= \tan^{-1} \left( \frac{\cos\left(\frac{\pi\tau}{T}\right)\sin\left(\frac{\pi\tau}{T}\right)}{V + \sin\left(\frac{\pi\tau}{T}\right)\sin\left(\frac{\pi\tau}{T}\right)} \right)$$

10

30

Thus, the amount of phase predistortion should be:

$$\varphi = -\theta$$

(11)

$$= -\tan^{-1} \left( \frac{\cos\left(\frac{\pi\tau}{T}\right)\sin\left(\frac{\pi\tau}{T}\right)}{V + \sin\left(\frac{\pi\tau}{T}\right)\sin\left(\frac{\pi\tau}{T}\right)} \right)$$

where  $\phi$  is the required phase predistortion for a non-centered PWM signal. Approximation of tan<sup>-1</sup> by Taylor series is

$$\tan^{-1}(x) = x - \frac{1}{3}x^3 + \frac{1}{3}x^5 - \frac{1}{7}x^7 \dots$$

$$\tan^{-1}(x) = x \text{ if } x \text{ is close to } `0` (12)$$

Since  $\theta$  converges to 0 if the integer part increases, as shown in FIG. 10-(b), equation (12) is valid as far as the integer part is large enough. With this approximation, equation (11) becomes a simple closed-form expression as follows:

$$\begin{split} \varphi &= -\tan^{-1} \Biggl( \frac{\cos\left(\frac{\pi\tau}{T}\right) \sin\left(\frac{\pi\tau}{T}\right)}{V + \sin\left(\frac{\pi\tau}{T}\right) \sin\left(\frac{\pi\tau}{T}\right)} \Biggr) \end{split} \tag{13}$$

$$\approx -\frac{\cos\left(\frac{\pi\tau}{T}\right) \sin\left(\frac{\pi\tau}{T}\right)}{V + \sin\left(\frac{\pi\tau}{T}\right) \sin\left(\frac{\pi\tau}{T}\right)}$$

$$\approx -\frac{\cos\left(\frac{\pi\tau}{T}\right) \sin\left(\frac{\pi\tau}{T}\right)}{V} = -\frac{1}{V} \cdot \cos\left(\frac{\pi\tau}{T}\right) \sin\left(\frac{\pi\tau}{T}\right)$$

$$if V \gg \sin\left(\frac{\pi\tau}{T}\right) \sin\left(\frac{\pi\tau}{T}\right)$$

Equation (13) implies that the phase predistortion LUT can be broken into two smaller LUTs and a multiplier. One LUT takes the integer word of the amplitude signal and calculates  $_{40}$

$$\frac{1}{V}$$

while the other LUT takes the fractional word and calculates

$$\cos\left(\frac{\pi\tau}{T}\right)\sin\left(\frac{\pi\tau}{T}\right).$$

The total amount of the phase compensation is the multiplication of those two outputs. In this way, the phase predistortion LUT can be implemented with less complexity. In a polar 55 transmitter, the LUT to compensate AM-PM distortion of RF PA is likely to already exist in the system. In this case, the LUT for

> 1  $\overline{V}$

can be combined with the existing AM-PM predistortion 65 LUT, and only a small LUT with the fractional word inputs calculating

$$\cos\left(\frac{\pi\tau}{T}\right)\sin\left(\frac{\pi\tau}{T}\right)$$

and a multiplier are required additionally.

The validity of equation (13) is confirmed, as shown in FIG. 11. The integer word is 10 bits, which ranges from 0 to 1023, and the fractional word is 5 bits (32 levels). The approximation in equation (13) agrees well with equation (11) when the input code is over 100 although they differ when the input code is less than 6. Note that the input code represents the amplitude of an input baseband signal in a polar transmitter although we are currently dealing with phase 15 compensation for non-centered PWM. For an EDGE signal, the input code is always larger than certain amplitude in order to keep its peak-to-minimum ratio as explained earlier. As a result, equation (13) is a very good approximation for EDGE, as verified by the later illustrated simulations.

The resolution of the phase path of a polar transmitter is another restriction to affect complexity of the entire system. The size of a phase predistortion LUT depends on not only the input resolution but also the output resolution, which goes into the phase input of a PLL. If an ADPLL is employed, the resolution of the phase input of an ADPLL also affects complexity of its building blocks, such as a DCO, a digital loop filter, and a TDC. The required phase resolution of the noncentered PWM method can be determined by simulations, and the results with different phase resolutions are presented later.

Note that the phase compensation 1200 for non-centered PWM should occur instantly (i.e., having wide enough bandwidth) as illustrated in FIG. 12. It means that an ADPLL should employ a special method such as a two-point modu-35 lation. R. B. Staszewski et al. in 'Just-in-time gain estimation of an RF digitally-controlled oscillator for digital direct frequency modulation', published in IEEE Trans. Circuits Syst. II, vol. 50, issue 11, pp. 887-892, November 2003 [10], which is incorporated herein by reference, employs a feed-forward path for an instant phase/frequency shift, and also uses a predistortion path to compensate closed-loop counteract; hence, the instant phase shift shown in FIG. 12 is possible. Amplitude Resolution Improvement Employing PWM

Given the previous analysis, the architecture for improving 45 the amplitude resolution of a polar transmitter employing a PWM generator will be described. The architecture for centered and non-centered PWM should differ because of their different characteristics. Firstly, we will discuss the architecture for centered PWM, as disclosed in [6], with the architecture for non-centered then introduced. A simple delay chain circuit, which can be used in a PWM generator, will be also described and its circuit-level simulation results will be shown. Finally, centered and non-centered PWM methods will be compared.

Architecture Employing Centered PWM

Referring now to FIG. 13, an example of an architecture 1300 of a polar transmitter with a PWM generator, which creates centered PWM signals, is illustrated in accordance with some example embodiments of the invention. Note that 60 the architecture 1300 is augmented from the original polar transmitter architecture depicted in FIG. 1. The building blocks drawn with the bold lines are added to the original polar transmitter to improve its amplitude resolution. In FIG. 13, the PWM generator 1302 generates 2<sup>N</sup>PWM-level centered PWM signals. The original amplitude signal is  $N_A$ -bit. The integer part is Nint bits, and it drives the DPA's switching transistors directly. The Nfrac-bit signals, which is the frac-

45

65

tional part of the amplitude signal, go into the amplitude predistortion LUT 1304 for centered PWM, which is realized based on equation (4). The LUT 1304 has N<sub>frac</sub>-bit inputs and  $N_{PWM}$ -bit outputs. It will occupy a very small area in modern CMOS processes because its size is only  $2^N$  frac words. In this example embodiment, we used a 5-bit fractional word as input and a 12-level centered PWM signal as output, which are represented by 32 4-bit data words in the predistortion LUT 1304. Therefore, the size of the required LUT for centered PWM is: 2<sup>5</sup>-word×4-bit=128-bit. Note that this LUT can also be merged with the LUT for DPA in the original polar transmitter so as to minimize the area.

Referring now to FIG. 14, an example of a conceptual block diagram 1400 of a centered PWM generator and its timing diagram are illustrated in accordance with some example embodiments of the invention. In one example, two pulse signals,  $d_1$  and  $d_2$ , are adjusted with two simple delay chains 1402 and 1404 in order to produce the desired pulse output.

In order to achieve better centering ability, a Pulse Center block 1306, 1406 in FIG. 13 and FIG. 14, which can be implemented with either a DLL or fine resolution delay lines, manipulates the main clock delay, thereby controlling the pulse position of the PWM signal. The Pulse Center block 1306/1406 plays an important role in that it keeps the position of the PWM at the center of the first half cycle of the carrier signal as depicted in FIG. 4(b) across process variation. If the PWM is not located at the center, it causes phase distortion of the output signal. Channel switching is another issue since pulse position is relative to the clock period T. Therefore, the relative pulse position changes if the clock period is changed. The Pulse Center block 1306/1406 can change the delay for the clock input of the PWM generator  $(clk_1)$  such that the pulse position is always centered no matter what TX channel 35 is selected.

Referring now to FIG. 15, an example of a polar transmitter 1500 with non-centered PWM, is illustrated in accordance with some example embodiments of the invention. The novel architecture is augmented from the original polar transmitter  $_{40}$ architecture in FIG. 1. In FIG. 15, the PWM generator makes 2<sup>N</sup>PWM-level non-centered PWM signals. The phase LUT 1502 takes the N<sub>frac</sub>-bit fractional word of the amplitude signal as an input, and it calculates

$$\cos\Bigl(\frac{\pi\tau}{T}\Bigr) \sin\Bigl(\frac{\pi\tau}{T}\Bigr),$$

as per equation (3). The  $N_{int}$ -bit integer word of the amplitude 50 signal goes to the building block 1504, which calculates the inverse. It could be an arithmetic logic or an LUT. In most commercial polar transmitter systems, there is an AM-PM LUT. Hence, the

1

block 1504 can be simply combined with the existing LUT.  $^{60}$ The combination of the phase LUT 1502 and the

in

block 1504 calculates the approximated phase predistortion value as explained earlier. The additional LUT 1506 for amplitude path is also used, and it takes the fractional word of the amplitude signal. The content of the LUT **1506** is derived according to equation (9), which is an approximation. Note that the Pulse Center block is unnecessary in this case because non-centered PWM is always aligned with the main clock as far as the PWM generator 1508 is referenced to the main clock.

Referring now to FIG. 16, an example of a conceptual block diagram 1600 of a non-centered PWM generator and its timing diagram is illustrated, in accordance with some example embodiments of the invention. In this case, the generated PWM is aligned with the rising edge of the main clock. If necessary, the building block in FIG. 16 can be easily modified such that the PWM is aligned with the falling edge of the clock instead of the rising edge. Then, the content of the amplitude and phase predistortion LUTs should be changed, but the overall architecture will remain the same. Note that 20 FIG. 16 requires only one delay chain 1602, as compared to the centered PWM generator shown in FIG. 14. Therefore, the architecture of FIG. 16 is much simpler overall to implement.

The PWM generators in FIG. 14 and FIG. 16 require a delay chain 1402/1404/1602 where the delay is controllable digitally. A simple inverter-based delay chain 1700 for the PWM generator is described in this section. FIG. 17 illustrates the described circuit. The inverters  $inv_1$ ,  $inv_2$ ,  $inv_3$ ,  $inv_4$ are cascaded, and their input nodes can be set to the desired logic levels by force in such a way that some inverters are held to a certain voltage while the others propagate signals from the previous stages. There are three possible states for each input node of the inverters  $inv_1$ -inv<sub>4</sub>: high, low, and local floating. When the input node of the inverter  $inv_1/inv_2/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/inv_3/$ inv4 is set to floating, the voltage of that node is determined by the previous stage; thus, that inverter inv<sub>1</sub>/inv<sub>2</sub>/inv<sub>3</sub>/inv<sub>4</sub> propagates a digital signal. By controlling the number of the inverters propagating a signal, one can change the total propagation delay of the circuit.

FIG. 18 illustrates how the described circuit creates four inverter delays 1800. In the reset state, the inputs of all four inverters  $inv_1$ -inv<sub>4</sub> are held at a certain voltage by pre-set devices at the input nodes of the inverters  $inv_1$ -inv<sub>4</sub> such that the delay chain's output is low. In order to generate four inverter delays, the inputs of the last three inverters inv2-inv4 are set to floating. Now, the first stage determines the output. Therefore, after the input of the first inverter  $inv_1$  goes to high, the signal propagates through the four inverters. The total delay is:

delay=tclk-to-start1+4.delayinv

where:  $delay_{inv}$  is an inverter delay, and  $t_{clk-to-start1}$  is the time to take for the input of inv1 to become high, which is the delay from the clock to the start of the signal.  $t_{clk-to-start1}$  is determined by the size of one of the pre-set devices,  $P_1$ , and the 55 total capacitance of the input node of  $inv_1$ .

FIG. 19 illustrates the case of a three inverter delay 1900. In order to create three inverter delays, the inputs of the last two inverters  $inv_3$  and  $inv_4$  become floating. When the input of the first two inverters inv, and inv, are set to high and low, respectively, the signal propagates through the last three inverters inv2-inv4 creating three inverter delays. Note that the input of  $inv_1$  is still low before  $t_{clk-to-start1}$ . Thus,  $inv_1$  attempts to make the output, which is the input of inv2, high before tclk-to-start1 while N<sub>2</sub> tries to make the input of inv<sub>2</sub> low. If N<sub>2</sub> is much larger than the size of inv<sub>1</sub>, then the input of inv<sub>2</sub> will become low by force even before t<sub>clk-to-start1</sub>. In this case, t<sub>clk-to-start2</sub> the time to take for the input of inv<sub>2</sub> to become low, will be