US009207646B2

# (12) United States Patent

Wang et al.

# (10) **Patent No.:**

US 9,207,646 B2

(45) **Date of Patent:**

Dec. 8, 2015

## (54) METHOD AND APPARATUS OF ESTIMATING/CALIBRATING TDC GAIN

(75) Inventors: Chi-Hsueh Wang, Kaohsiung (TW);

Robert Bogdan Staszewski, Delft (NL); Yi-Hsien Cho, Hsinchu County (TW)

(73) Assignee: MEDIATEK INC., Science-Based

Industrial Park, Hsin-Chu (TW)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 519 days.

(21) Appl. No.: 13/610,842

(22) Filed: Sep. 11, 2012

(65) Prior Publication Data

US 2013/0191061 A1 Jul. 25, 2013

### Related U.S. Application Data

- (60) Provisional application No. 61/589,018, filed on Jan. 20, 2012.

- (51) Int. Cl.

**G04F 10/06** (2006.01) **G04F 10/00** (2006.01)

(52) U.S. Cl.

CPC ...... *G04F 10/005* (2013.01)

(58) Field of Classification Search

# (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,429,693    | B1   | 8/2002  | Staszewski     |      |

|--------------|------|---------|----------------|------|

| 7,427,940    | B2   | 9/2008  | Staszewski     |      |

| 7,482,956    | B2   | 1/2009  | Huang          |      |

| 7,940,099    | B2   | 5/2011  | Weltin-Wu      |      |

| 8,000,428    | B2   | 8/2011  | Staszewski     |      |

| 8,090,068    | B2   | 1/2012  | Sun            |      |

| 8,198,929    | B2   | 6/2012  | Pellerano      |      |

| 8,669,890    | B2 * | 3/2014  | Wang et al 341 | /118 |

| 2011/0227621 | A1*  | 9/2011  | Ridgers 327    | /159 |

| 2011/0267120 | A1   | 11/2011 | Ravi           |      |

| 2013/0002317 | A1   | 1/2013  | Frantzeskakis  |      |

| 2013/0033293 | A1*  | 2/2013  | Zhang 327      | /156 |

#### FOREIGN PATENT DOCUMENTS

| CN | 101414821 A   | 4/2009  |

|----|---------------|---------|

| CN | 102017421 A   | 4/2011  |

| CN | 102217198 A   | 10/2011 |

| WO | 2007093222 A1 | 8/2007  |

<sup>\*</sup> cited by examiner

Primary Examiner — Toan Le

(74) Attorney, Agent, or Firm — Winston Hsu; Scott Margo

# (57) ABSTRACT

A method of estimating gain of a time-to-digital converter (TDC) includes: capturing a TDC output sample; calculating a gradient in response to the TDC output sample; and adjusting a TDC normalizing gain based on the calculating step. Another method of calibrating gain of a TDC includes: capturing a phase error which is derived from a TDC output sample, a reference phase and a variable phase; calculating a gradient in response to the phase error; and adjusting a TDC normalizing gain based on the calculating step.

### 28 Claims, 8 Drawing Sheets

FIG. 2

FIG. 5

FIG. 7

FIG. 8

# METHOD AND APPARATUS OF ESTIMATING/CALIBRATING TDC GAIN

# CROSS REFERENCE TO RELATED APPLICATIONS

This application claims the benefit of U.S. provisional application No. 61/589,018, filed on Jan. 20, 2012 and incorporated herein by reference.

#### BACKGROUND

The disclosed embodiments of the present invention relate to a time-to-digital converter (TDC) which may be part of an all-digital phase-locked loop, and more particularly, to a method of estimating/calibrating the TDC gain and a related apparatus.

All-digital phase-locked loop (ADPLL) is a very attractive technique for a multi-radio system on chip (SOC). It results in 20 the smaller occupied circuit area and lower power consumption, especially compared with the analog PLL circuit. For example, an ADPLL includes a digitally-controlled oscillator (DCO), a time-to-digital converter (TDC), and a digital loop filter. The TDC is an important circuit module used to mea- 25 sure timestamp, and the measurement result is a finite-length digital word. The TDC used in the ADPLL acts as a phase/ frequency detector and a charge pump used in the analog PLL. Taking the advantage of the digital implementation, the TDC is easily to be programmed and calibrated, which makes it very suitable for the ADPLL. Recently, due to development of the deep-submicron CMOS technology, the TDC may be implemented utilizing a simple inverter chain, with each inverter providing a stable delay. As the TDC is a key component of the ADPLL, the gain and linearity performance of 35 the TDC significantly affects the quality of the ADPLL. There is a need for an innovative design which can calibrate the TDC gain and nonlinearity precisely without adding too many extra detection and compensation circuits.

### **SUMMARY**

In accordance with exemplary embodiments of the present invention, a method of estimating/calibrating the TDC gain and a related apparatus are proposed to solve the above-45 mentioned problem.

According to a first aspect of the present invention, an exemplary method of estimating gain of a time-to-digital converter (TDC) includes: capturing a TDC output sample; calculating a gradient in response to the TDC output sample; 50 and adjusting a TDC normalizing gain based on the calculating step.

According to a second aspect of the present invention, an exemplary method of estimating gain of a time-to-digital converter (TDC) includes: capturing a phase error derived 55 from a TDC output sample, a reference phase and a variable phase; calculating a gradient in response to the phase error; and adjusting a TDC normalizing gain based on the calculating step.

According to a third aspect of the present invention, an 60 exemplary apparatus of estimating gain of a time-to-digital converter (TDC) is provided. The exemplary apparatus includes a capturing circuit and a gain adjusting circuit. The capturing circuit is arranged for capturing a TDC output sample. The gain adjusting circuit is arranged for calculating 65 a gradient in response to the TDC output sample, and adjusting a TDC normalizing gain based on the gradient.

2

According to a fourth aspect of the present invention, an exemplary apparatus of calibrating gain of a time-to-digital converter (TDC) is provided. The exemplary apparatus includes a capturing circuit and a gain adjusting circuit. The capturing circuit is arranged for capturing a phase error which is derived from a TDC output sample, a reference phase and a variable phase. The gain adjusting circuit is arranged for calculating a gradient in response to the phase error, and adjusting a TDC normalizing gain based on the gradient.

These and other objectives of the present invention will no doubt become obvious to those of ordinary skill in the art after reading the following detailed description of the preferred embodiment that is illustrated in the various figures and drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

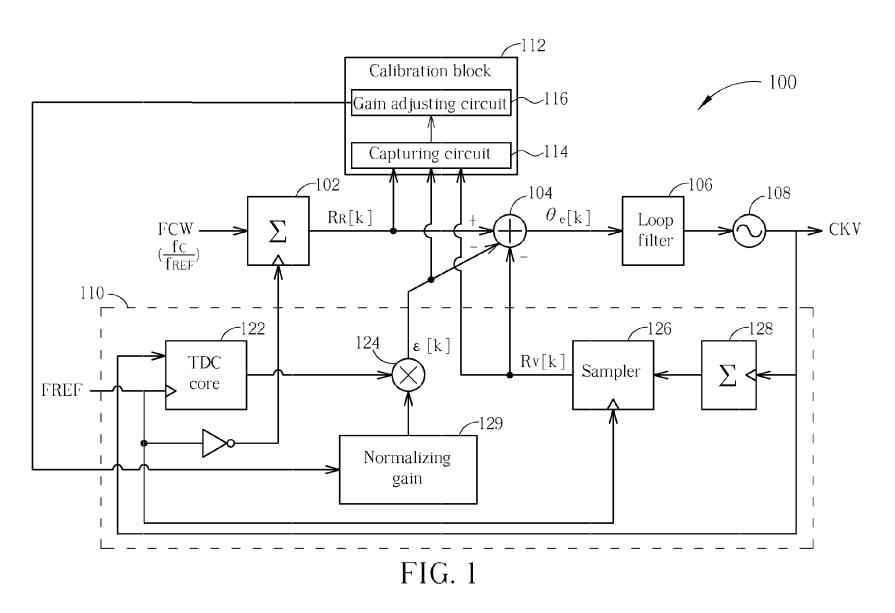

FIG. 1 is a diagram illustrating an ADPLL according to a first exemplary embodiment of the present invention.

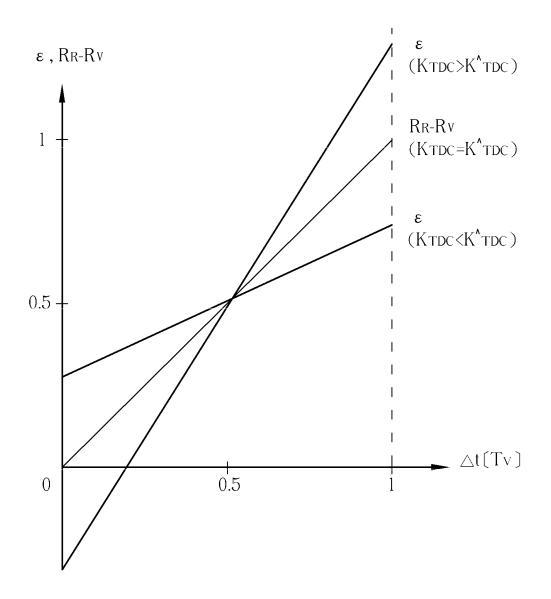

FIG. 2 is a diagram illustrating the effect of the TDC normalizing gain error.

FIG. 3 is a diagram illustrating an ADPLL according to a second exemplary embodiment of the present invention.

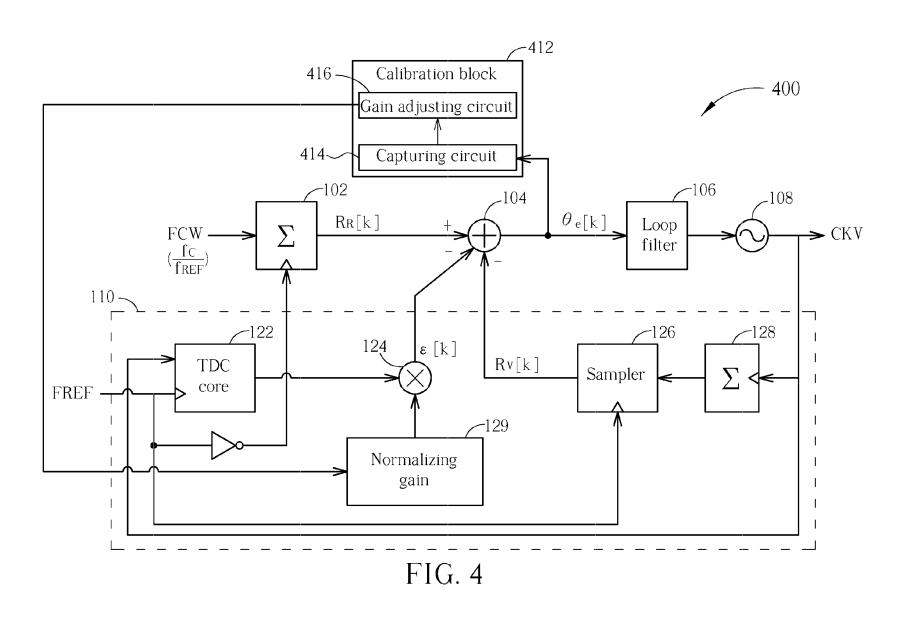

FIG. 4 is a diagram illustrating an ADPLL according to a third exemplary embodiment of the present invention.

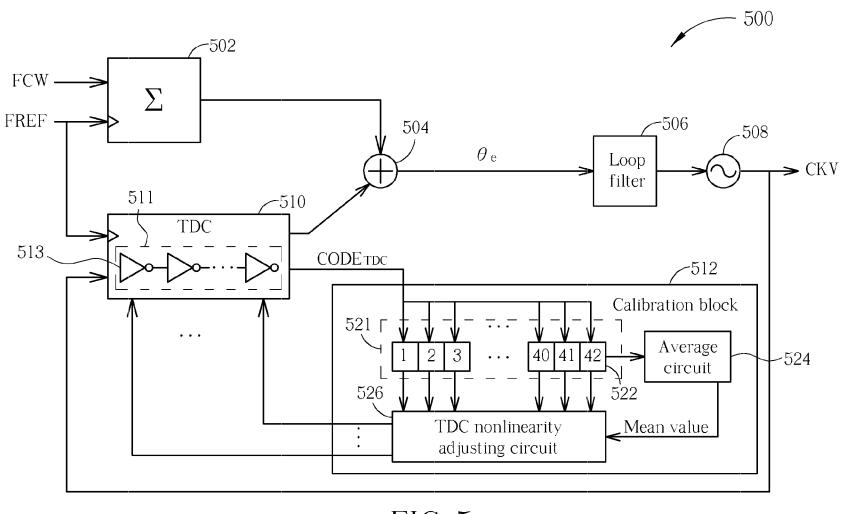

FIG. 5 is a diagram illustrating an ADPLL according to a fourth exemplary embodiment of the present invention.

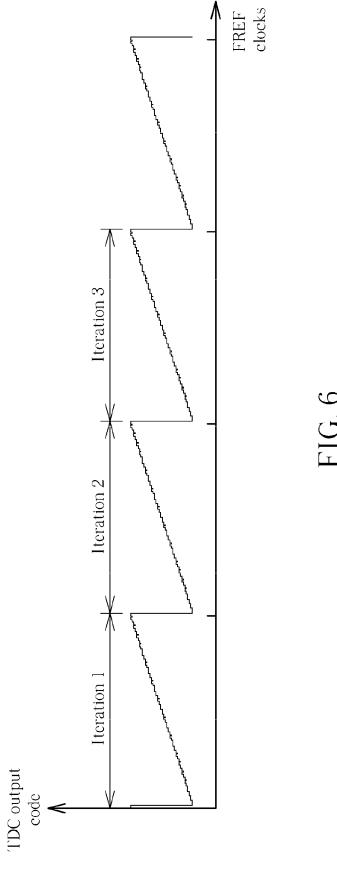

FIG. 6 is a diagram illustrating the relation between the clock cycles of the frequency reference clock and the value of the TDC output code.

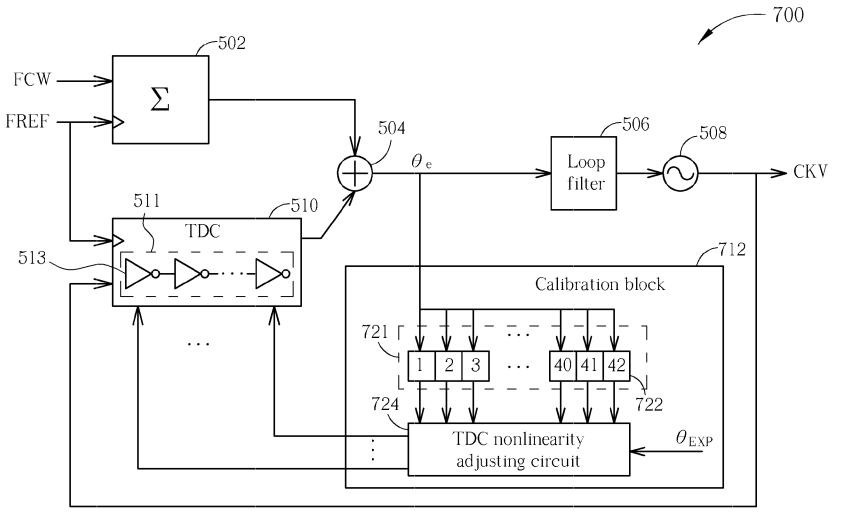

FIG. 7 is a diagram illustrating an ADPLL according to a fifth exemplary embodiment of the present invention.

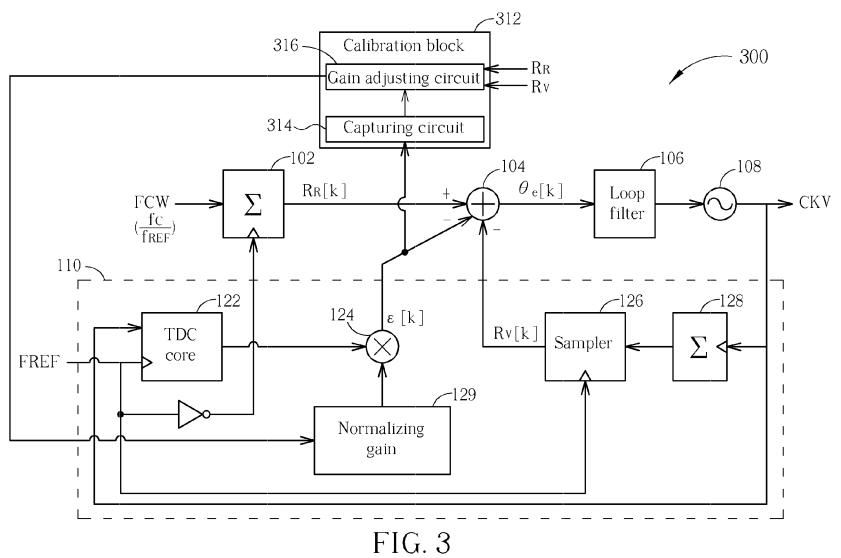

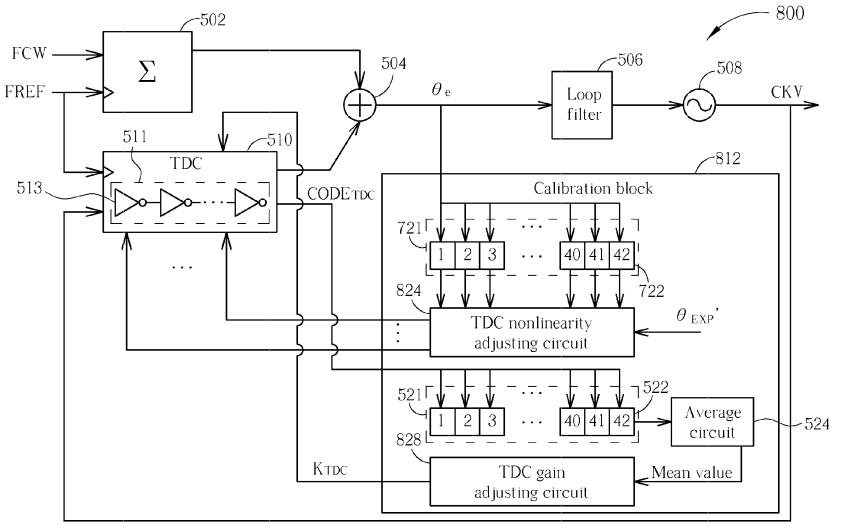

FIG. **8** is a diagram illustrating an ADPLL according to a sixth exemplary embodiment of the present invention.

#### DETAILED DESCRIPTION

Certain terms are used throughout the description and following claims to refer to particular components. As one skilled in the art will appreciate, manufacturers may refer to a component by different names. This document does not intend to distinguish between components that differ in name but not function. In the following description and in the claims, the terms "include" and "comprise" are used in an open-ended fashion, and thus should be interpreted to mean "include, but not limited to . . . ". Also, the term "couple" is intended to mean either an indirect or direct electrical connection. Accordingly, if one device is coupled to another device, that connection may be through a direct electrical connection, or through an indirect electrical connection via other devices and connections.

FIG. 1 is a diagram illustrating an ADPLL according to a first exemplary embodiment of the present invention. The exemplary ADPLL 100 includes an accumulator 102, an adder (performing a subtraction operation) 104, a loop filter 106, a digitally-controlled oscillator (DCO) 108, a TDC 110, and a calibration block 112, where the TDC 110 includes a TDC core 122, a multiplier 124, a sampler 126, and an accumulator 128, and the calibration block 112 includes a capturing circuit 114 and a gain adjusting circuit 116. It should be noted that only the elements pertinent to the present invention are shown in FIG. 1. The ADPLL 100 may have additional elements included therein, depending upon actual design requirement/consideration. The accumulator 102 is clocked by a frequency reference clock FREF with a fixed frequency f<sub>REF</sub> (e.g., 26 MHz), and arranged for accumulating a frequency command word FCW according to the frequency

reference clock FREF. As shown in FIG. 1, the accumulator 102 is clocked by falling edges of the frequency reference clock FREF, and the frequency command word FCW is set by  $f_c/f_{REF}$ , where  $f_c$  is a nominal carrier frequency of the output clock CKV of the DCO 108. Therefore, the reference phase 5  $R_R$  is increased by an increment value  $f_c/f_{REF}$  each time the accumulator 102 is clocked by one falling edge of the frequency reference clock FREF. The TDC 110 is arranged for generating a TDC output sample (i.e., a normalized TDC output code) E and a variable phase  $R_{\nu}$ . Specifically, the accumulator 128 is clocked by the output clock CKV for counting clock cycles of the output clock CKV and accordingly generates an accumulated result. In this embodiment, the sampler 126 is clocked by rising edges of the frequency reference clock FREF. Therefore, the sampler **126** samples the accumulated result generated by the accumulator 128 and outputs one sampled value as the variable phase R<sub>V</sub> each time the sampler 126 is clocked by one rising edge of the frequency reference clock FREF. The TDC core 122 generates a TDC output code according to the output clock CKV and the fre- 20 quency reference clock FREF. For example, the TDC core 122 may be implemented using an inverter delay chain which includes a plurality of cascaded inverters acting as TDC cells. The multiplier 124 is arranged to multiply the TDC output code with the TDC normalizing gain 129 and accordingly 25 generate the normalized TDC output code E. The TDC normalizing gain 129 needs to be an inverse of the TDC step size or TDC gain, which is a physical parameter of the TDC in units of ps, multiplied by a constant such that the multiplier **124** output is a fixed point number between 0.0 and 1.0 for the 30 full range (i.e.,  $0-T_{\nu}$ ) of the TDC input. Hence, since the TDC gain and the optimal value of the TDC normalizing gain 129 are the mathematical inverse of each other, these terms are used interchangeably: knowing the TDC gain gives the mathematically precise value of the multiplier 129, and having an 35 estimate of the normalizing gain (multiplier 129) allows to also estimate the TDC gain. From the operational viewpoint the normalizing the TDC gain is as follows: Initially, the TDC gain is not known since it is the subject of the process, voltage and temperature variations. Hence, an estimate is used as a 40 starting point of the calibration process. The calibration process can estimate the TDC step size and then calculate its inverse to arrive at the TDC normalizing gain. Alternatively, the calibration process can iteratively arrive at the most optimal value of the TDC normalizing gain multiplier, in which 45 case knowledge of its inverse, i.e., the TDC gain might not be required. The loop filter 106 generates a digital control value to the DCO 108 according to a phase error  $\theta_e$  generated from the adder 104. For example, the phase error  $\theta_e$  with the discrete-time index k may be expressed as below.

$$\Theta e[k] = R_R[k] - R_V[k] - \epsilon[k] \tag{1}$$

As the present invention focuses on calibrating the TDC normalizing gain 129, details of the TDC 110 are omitted here for brevity. It should be noted that the TDC implementation 55 shown in FIG. 1 is for illustrative purposes only, and is not meant to be a limitation of the present invention. For example, a retiming mechanism may be employed to generate a retimed frequency reference clock by using rising edges of the output clock CKV to sample the frequency reference clock FREF. 60 Hence, the retimed frequency reference clock is used to take place of the frequency reference clock FREF received by the sampler 126 and the accumulator 102. Details of the traditional ADPLL can be found in a book: R. B. Staszewski and P. T. Balsara, "All-Digital Frequency Synthesizer in Deep-65 Submicron CMOS", New Jersey: John Wiley & Sons, Inc., 261 pages, ISBN: 978-0471772552, September 2006.

4

The capturing circuit 114 of the calibration block 112 is arranged for capturing the reference phase R<sub>R</sub>, the TDC output sample  $\epsilon$  and the variable phase  $R_{\nu}$ , and the gain adjusting circuit 116 of the calibration block 112 is arranged for adjusting the TDC normalizing gain 129 in response to the captured reference phase  $R_R$ , TDC output sample  $\epsilon$  and variable phase  $R_{\nu}$ . Specifically, the gain adjusting circuit 116 of the calibration block 112 derives a gradient from calculating a difference between a slope of the TDC output sample, such as slope( $\epsilon$  $[k]-\epsilon[k-1]$ ), and a slope of a difference between the reference phase and the variable phase, such as slope( $(R_R[k]-R_V[k])$ - $(R_R[k-1]-R_v[k-1])$ , and continuously/iteratively updates the TDC normalizing gain 129 based on the calculated gradient. As the gradient is taken as an error function, the calibration block 112 will stochastically reduce the error of the TDC normalizing gain 129.

Please refer to FIG. 2, which is a diagram illustrating the effect of the TDC normalizing gain error. It plots two components (and  $R_R$ - $R_V$ ) of the digital phase error versus the input time difference in the units of the nominal DCO period  $(T_{\nu})$ . The plot also accounts for zeroing out of the phase error, which is the expected long-term operation of the type-II ADPLL-loop. As mentioned above, the TDC normalizing gain 129 is used to normalize the TDC output code generated from the TDC core 122. Hence, the TDC normalizing gain 129 changes the slope of the TDC output sample  $\epsilon$ . The output clock CKV may have frequency variation due to TDC normalizing gain error. However, as the sampling rate of the sampler 126 is lower than the clock rate of the output clock CKV, the variation of the variable phase  $R_{\nu}$  may be mitigated/ avoided due to accumulation performed by the accumulator 128. As mentioned above, the DCO 108 adjusts the output clock CKV in response to the phase error  $\theta_e$  (e.g.,  $\theta_e = R_R$  $R_{\nu} - \epsilon$ ). Assuming the ADPLL loop is settled and operates in type-II, the slope of the TDC output sample  $\epsilon$  should match the slope of the  $R_R$ - $R_V$  value when the TDC normalizing gain 129 is set by a value  $K_{TDC}$  equal to a correct value (i.e., an ideal value)  $K_{TDC,0}$ . In a case where the slope of the TDC output sample  $\epsilon$  is found larger than the slope of the  $R_R - R_V$ value, this implies that the TDC normalizing gain 129 is set by a value  $K_{TDC}$  larger than the correct value  $K_{TDC,0}$ . In another case where the slope of the TDC output sample  $\epsilon$  is found smaller than the slope of the  $R_R$ - $R_V$  value, this implies that the TDC normalizing gain 129 is set by a value  $K_{TDC}$  smaller than the correct value  $K_{TDC,0}$ . To put it another way, there is a positive correlation between the TDC normalizing gain error and the fractional number of the  $R_R$ - $R_V$  value, and the slope of the  $R_R$ - $R_V$  value is related to the fractional number of the  $R_R$ - $R_V$  value.

By monitoring the gradient derived from  $slope(\epsilon)$ -slope  $(R_R - R_{\nu})$ , the gain adjusting circuit **116** of the calibration block **112** easily knows how to adjust the TDC normalizing gain **129**. For example, the gain adjusting circuit **116** subtracts an adjustment step value from the current gain value  $K_{TDC}$  for decreasing the TDC normalizing gain **129** when the gradient has a positive sign, and adds an adjustment step value to the current gain value  $K_{TDC}$  for increasing the TDC normalizing gain **129** when the gradient has a negative sign.

Regarding the above-mentioned example, the gain adjusting circuit 116 of the calibration block 112 utilizes captured TDC output sample  $\epsilon$ , captured reference phase  $R_R$  and captured variable phase  $R_{\nu}$  to estimate the gradient which is referenced to control the TDC gain calibration. In an alternative design of the present invention, the reference phase and the variable phase may be set by expected values directly. In other words, the aforementioned slope( $R_R - R_{\nu}$ ) may be regarded as a predetermined value since the difference

between the expected reference phase and the expected variable phase is known beforehand.

Please refer to FIG. 3, which is a diagram illustrating an ADPLL according to a second exemplary embodiment of the present invention. A capturing circuit 314 of the calibration 5 block 312 of the ADPLL 300 captures the TDC output sample € generated from the TDC 110, and a gain adjusting circuit 316 of the calibration block 312 utilizes the captured TDC output sample  $\epsilon$  as well as expected values  $R_R$ ,  $R_V$  of the reference phase and the variable phase for obtaining the gradient. As can be readily known from the following equation (2), the gradient may be calculated by  $slope(\epsilon)-slope(R_R$  $R_{\nu}$ ), where slope( $R_{R}$ - $R_{\nu}$ ) is a predetermined (calculated) dynamically-changing value, and  $slope(\epsilon)$  is dynamically calculated in response to the captured TDC output samples. 15 The same objective of stochastically reducing the TDC normalizing gain error by iteratively adjusting the TDC normalizing gain 129 based on the calculated gradient is achieved.

Various iterative methods well known in the field of adaptive signal processing, such as least mean square (LMS) algorithms, may be used. By way of example, a sign-sign LMS algorithm may be used by the gain adjusting circuit 116/316 of the calibration block 112/312.

As mentioned above, the phase error  $\theta_e$  is equal to  $R_R - R_V - \epsilon$ . Hence, the gradient, which is the difference between successive phase error samples (e.g.,  $\theta_e[k]$  and  $\theta_e[k-1]$ ) may be obtained using following equation.

$$\begin{array}{ll} \theta_{e}[k] - \theta_{e}[k-1] = (R_{R}[k] - R_{V}[k] - \epsilon[k]) - (R_{R}[k-1] - R_{V}[k-1] - \epsilon[k-1]) = [(R_{R}[k] - R_{V}[k]) - (R_{R}[k-1] - R_{V}[k-1]) - (\epsilon[k] - \epsilon[k-1]) \end{array} \tag{2}$$

Therefore, the phase error  $\theta_e$  also gives information correlated with the TDC normalizing gain error, and may be used for controlling the TDC gain calibration. Please refer to FIG. 4, which is a diagram illustrating an ADPLL according to a 35 third exemplary embodiment of the present invention. A capturing circuit 414 of the calibration block 412 of the ADPLL **400** captures the phase error  $\theta_e$ , and a gain adjusting circuit 416 of the calibration block 412 calculates a gradient in response to the captured phase error  $\theta_e$ . When the gradient has 40 a positive sign, this implies that the slope of the TDC output sample  $\epsilon$  is smaller than the slope of the  $R_R - R_V$  value, and the TDC normalizing gain 129 has a value  $K_{TDC}$  smaller than the correct value K<sub>TDC,0</sub>. Therefore, the gain adjusting circuit 416 of the calibration block 412 adds an adjustment step value 45 to the current gain value K<sub>TDC</sub> for increasing the TDC normalizing gain 129. When the gradient value has a negative sign, this implies that the slope of the TDC output sample  $\epsilon$  is larger than the slope of the  $R_R$ - $R_V$  value, and the TDC normalizing gain 129 has a value  $K_{TDC}$  larger than the correct 50 value  $K_{TDC,0}$ . Therefore, the gain adjusting circuit 416 of the calibration block 412 subtracts an adjustment step value from the current gain value  $K_{T\!DC}$  for decreasing the TDC normalizing gain 129. The same objective of stochastically reducing the TDC normalizing gain error by iteratively adjusting the 55 TDC normalizing gain 129 based on the calculated gradient is achieved. Naturally, the stochastic iterative method could also be sign-value or sign-sign, which is well known in the field of adaptive signal processing. Various iterative methods well known in the field of adaptive signal processing, such as 60 least mean square (LMS) algorithms, may be used. By way of example, a sign-sign LMS algorithm may be used by the gain adjusting circuit 416 of the calibration block 412.

The linearity performance of the TDC may also affect the quality of the ADPLL. Hence, the TDC cell mismatch is also needed to be well accounted for to avoid the degradation of the ADPLL performance. The present invention further pro-

6

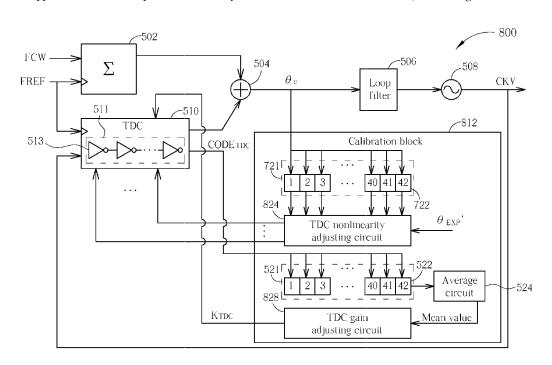

poses a TDC nonlinearity calibration scheme. Please refer to FIG. 5, which is a diagram illustrating an ADPLL according to a fourth exemplary embodiment of the present invention. The exemplary ADPLL 500 includes an accumulator 502, an adder 504, a loop filter 506, a DCO 508, a TDC 510, and a calibration block 512. It should be noted that only the elements pertinent to the present invention are shown in FIG. 5. The ADPLL 500 may have additional elements included therein, depending upon actual design requirement/consideration. The accumulator 502 is clocked by a frequency reference clock FREF with a fixed frequency  $f_{REF}$  (e.g., 26 MHz), and arranged for accumulating a frequency command word FCW set by  $f_c/f_{REF}$ , where  $f_c$  is a nominal carrier frequency of the output clock CKV of the DCO 508, and the frequency command word FCW is a fixed value composed of an integer number and a fractional number (e.g., 1/1000 or 1/10000). Therefore, an accumulator output is increased by the fixed value representative of  $f_c/f_{REF}$  each time the accumulator 502 is clocked by the frequency reference clock FREF. The TDC 510 is arranged for generating a TDC output (e.g., a normalized TDC code) to the adder 504, where the TDC 510 has a TDC core 511 including a plurality of TDC cells (e.g., inverters) 513 cascaded in series, and the TDC core 511 generates a TDC output code  $CODE_{TDC}$ . Based on setting of the fractional number of the frequency command word FCW, the digital value of the TDC output code CODE<sub>TDC</sub> is expected to increase from a minimum value to a maximum value gradually, and could be clipped at the maximum value when an overflow occurs. FIG. 6 is a diagram illustrating the relation between clock cycles of the frequency reference clock FREF and the digital value of the TDC output code CODE<sub>TDC</sub>. Assuming that the fractional number of the frequency command word FCW is set to a small value of 1/1000, one TDC output code  $\mathrm{CODE}_{T\!DC}$  is generated for a number of FREF clock cycles, and the TDC output code  $CODE_{TDC}$  is gradually increased from a minimum value to a maximum value with 1000 clock cycles of the frequency reference clock FREF.

The loop filter 506 generates a digital control value to the DCO 508 according to a phase error  $\theta_e$  generated from outputs of the accumulator 502 and the normalized TDC 510. The cell delay of one TDC cell 513 may be different from the cell delay of another TDC cell 513. Such a mismatch can be systematic (due to layout/geometry) and/or random (impurity doping fluctuation, edge roughness), thus resulting in TDC nonlinearity. The TDC cell mismatch would degrade accuracy of the TDC output code  $CODE_{TDC}$ . Therefore, the calibration block 512 is employed for performing TDC nonlinearity calibration by accounting for the cell delay of each TDC cell **513** implemented in the TDC **510**. Such accounting for can be realized as a small additive or multiplicative adjustment in calculating at the TDC unit granularity. By way of example, but not limitation, the TDC 510 in this embodiment may be configured to have 42 TDC cells 513. A capturing circuit **521** of the calibration block **512** captures each TDC output code sample (i.e., a TDC value carried by the TDC output code  $CODE_{TDC}$ ), and uses 42 multi-bit registers 522 to record accumulation values respectively, where each accumulation value indicates the number of times a specific sampled TDC value is carried by the TDC output code  $\mathrm{CODE}_{TDC}$ . For example, the register 522 indexed by "1" is used to record the number of times the TDC output code sample has the TDC value equal to 1, the register indexed by "2" is used to record the number of times the TDC output code sample has the TDC value equal to 2, and so on. The accumulation value is indicative of the cell delay length of the corresponding TDC cell. This is straightforward in case the TDC input is linearly swept with constant slope; it can be also

understood stochastically when the TDC input is random with flat statistical distribution. The calibration block **512** includes a calculating circuit, such as an average circuit **524** for calculating a mean value of the accumulation values stored in the registers **522**. If each of the accumulation values is equal to the same mean value after cell delays of the TDC cells **513** are properly calibrated, this implies that each of the TDC cells has the same cell delay and the mismatch between TDC cells is eliminated.

As shown in FIG. 5, the calibration block 512 further 10 includes a TDC nonlinearity adjusting circuit 526 arranged to adjust/account for a cell delay of a TDC cell by referring to the mean value and a corresponding accumulation value. For example, the difference between the mean value and the accumulation value stored in the register 522 indexed by "1" is used by the TDC nonlinearity adjusting circuit 526 to adjust/ account for a cell delay of a leading TDC cell (i.e., 1<sup>st</sup> TDC cell) included in the inverter delay chain. It should be noted that the closed loop would try to compensate the mismatch error of one bit (i.e., one TDC cell) using next bits (i.e., next 20 TDC cells), and the mismatch error will propagate to next several bits. Therefore, the cascaded TDC cells 513 of the inverter delay chain should be sequentially calibrated from the leading TDC cell (i.e., the left-most TDC cell 513 shown in FIG. 5) to the last TDC cell (i.e., the right-most TDC cell **513** shown in FIG. **5**). Hence, at the end of the first iteration shown in FIG. 6, the registers 522 store accumulation values respectively, the mean value can be obtained by the average circuit 524, and the TDC nonlinearity adjusting circuit 526 is operative to adjust a cell delay of the leading TDC cell 513 to 30 make the accumulation value recorded in the register 522 indexed by "1" approach the mean value, thus reducing or eliminating the mismatch error propagated to the next TDC cell in the next iteration (i.e., the second iteration). At the end of the second iteration shown in FIG. 6, the registers 522 store 35 accumulation values respectively, and the TDC nonlinearity adjusting circuit 526 is operative to adjust a cell delay of the next TDC cell 513 cascaded to the leading TDC cell 513 to make the accumulation value recorded in the register 522 indexed by "2" approach the same mean value, thus reducing 40 or eliminating the mismatch error propagated to the next TDC cell in the next iteration (i.e., the third iteration). As a person skilled in the pertinent art can readily understand the cell delay adjusting operation applied to following TDC cells included in the inverter delay chain, further description is 45 omitted here for brevity. The above-mentioned TDC mismatch calibration may be repeated by re-calculating a mean value after all of the TDC cells 513 have been calibrated. In this way, the calibration block 512 is capable of reducing the TDC mismatch stochastically.

Regarding the calibration block **512** shown in FIG. **5**, it is capable of adjusting correction gain of the normalized TDC **510**. In one exemplary design, adjusting the correction gain of the normalized TDC **510** may be accomplished through applying additive adjustment to a normalized TDC output. In sanother exemplary design, adjusting the correction gain of the normalized TDC **510** may be accomplished through adjusting a cell delay of a TDC cell. For example, the TDC has a plurality of TDC cells cascaded in series, and the TDC nonlinearity adjusting circuit **526** may be configured to adjust a cell delay of a first TDC cell prior to adjusting a cell delay of a second TDC cell following the first TDC cell prior to adjusting a normalized TDC output of the second TDC cell following the first TDC cell following the first TDC cell following the first TDC cell following

Please refer to FIG. 7, which is a diagram illustrating an ADPLL according to a fifth exemplary embodiment of the

8

present invention. The major difference between ADPLL 600 and ADPLL 700 is that the calibration block 712 of the ADPLL 700 is arranged to capture the phase error samples. Hence, a capturing circuit 721 of the calibration block 712 uses 42 registers 722 to record phase error samples each corresponding to one of the TDC cells 513. For example, the register 722 indexed by "1" is used to record a phase error sample which is captured when the current TDC output code has the TDC value equal to 1, the register 722 indexed by "2" is used to record a phase error sample which is captured when the current TDC output code has the TDC value equal to 2, and so on. The phase error sample is indicative of the cell delay length of the corresponding TDC cell. As shown in FIG. 7, the calibration block 712 further includes a TDC nonlinearity adjusting circuit 724 arranged to adjust a cell delay of a TDC cell by referring to difference between the captured phase error samples and an expected value  $\theta_{EXP}$  of the captured phase error samples. In this embodiment, the expected value  $\theta_{EXP}$  is based according to an unadjusted output of the TDC **510**. For example, the expected value  $\theta_{EXP}$  is set under the condition where the TDC normalizing gain error and cell delay mismatch of the TDC 510 are not compensated yet. Thus, the expected value  $\theta_{\text{EXP}}$  includes the expected phase error resulting from the TDC normalizing gain error. In other words, the expected value  $\theta_{EXP}$  is not equal to zero.

If each of the captured phase error samples is equal to the same expected value  $\theta_{EXP}$  after the cell delays of the TDC cells 513 are calibrated, this implies that each of the TDC cells 513 has the same cell delay and the mismatch between TDC cells is eliminated or non-existent. Therefore, the difference between the expected value  $\theta_{EXP}$  and the phase error sample stored in the register 722 indexed by "1" is used by the TDC nonlinearity adjusting circuit 724 to adjust a cell delay of a leading TDC cell (i.e., 1st TDC cell) included in the inverter delay chain. Similarly, as the closed loop would try to compensate the mismatch error of one bit (i.e., one TDC cell) using next bits (i.e., next TDC cells) and the mismatch error will propagate to next several bits, the cascaded TDC cells 513 of the inverter delay chain should be sequentially calibrated from the leading TDC cell (i.e., the left-most TDC cell 513 shown in FIG. 7) to the last TDC cell (i.e., the right-most TDC cell 513 shown in FIG. 7). Hence, when the captured phase error sample corresponds to the leading TDC cell (i.e., the left-most TDC cell 513 shown in FIG. 7), the TDC nonlinearity adjusting circuit 724 would adjust the cell delay of the leading TDC cell to make the captured phase error approach the expected value  $\theta_{EXP}$ , thus reducing or eliminating the mismatch error propagated to the next TDC cell in the same iteration (e.g., the first iteration shown in FIG. 6); and when the phase error sample corresponds to the next TDC cell following the leading TDC cell is captured, the TDC nonlinearity adjusting circuit 724 would adjust the cell delay of the next TDC cell following the leading TDC cell to make the captured phase error approach the same expected value  $\theta_{EXP}$ , thus reducing or eliminating the mismatch error propagated to the next TDC cell in the same iteration (e.g., the first iteration shown in FIG. 6). As a person skilled in the pertinent art can readily understand the cell delay adjusting operation applied to the following TDC cells, further description is omitted here for brevity. The TDC nonlinearity adjusting circuit 724 may adjust the cell delays of all TDC cells 513 during one iteration shown in FIG. 6, and adjust the cell delays of all TDC cells 513 again during another iteration shown in FIG. 6. In this way, the calibration block 712 is capable of reducing the TDC mismatch stochastically.

In the example shown in FIG. 7, the expected value  $\theta_{EXP}$  is based according to an unadjusted output of the TDC **510**.

Alternatively, the expected value may be based according to an adjusted output of the TDC 510. For example, an expected value  $\theta_{EXP}$  is set under the condition where the TDC normalizing gain error of the TDC 510 has been compensated. Thus, when the expected value  $\theta_{EXP}$  is properly set, the resulting 5 expected value  $\theta_{EXP}$  does not include the expected phase error resulting from the TDC normalizing gain error. Please refer to FIG. 8, which is a diagram illustrating an ADPLL according to a sixth exemplary embodiment of the present invention. The calibration block 812 of the ADPLL 800 includes a TDC nonlinearity adjusting circuit 824, a TDC gain adjusting circuit 828, and the aforementioned registers 722, 522 and average circuit 524. In this embodiment, the mean value generated from the average circuit 524 is used by the TDC gain adjusting circuit **828** for setting the normalizing gain  $K_{TDC}$  of the TDC 510. Therefore, the expected value  $\theta_{EXP}$ ' may be set without considering the expected phase error resulting from the TDC normalizing gain error. For example, the expected value  $\theta_{EXP}$ ' may be set by zero. The TDC nonlinearity adjusting circuit **824** is arranged to adjust a cell delay 20 of a TDC cell by referring to difference between the captured phase error samples stored in the registers 722 and the expected value  $\alpha_{EXP}$  of the captured phase error samples. As the function of the TDC nonlinearity adjusting circuit 824 is the same as that of the TDC nonlinearity adjusting circuit **724**, 25 further description is omitted here for brevity. The same objective of reducing the TDC mismatch stochastically is achieved by using the calibration block 812.

In above examples, the calibration block 712/812 is capable of adjusting correction gain of the normalized TDC 30 510. In one exemplary design, adjusting the correction gain of the normalized TDC 510 may be accomplished through adjusting a TDC normalizing gain. In another exemplary design, adjusting the correction gain of the normalized TDC 510 may be accomplished through applying additive adjust- 35 ment to a normalized TDC output. In yet another exemplary design, adjusting the correction gain of the normalized TDC 510 may be accomplished through adjusting a cell delay of a TDC cell. For example, the TDC has a plurality of TDC cells cascaded in series, and the TDC nonlinearity adjusting circuit 40 all-digital phase-locked loop (ADPLL). 724/824 may be configured to adjust a cell delay of a first TDC cell prior to adjusting a cell delay of a second TDC cell following the first TDC cell, or adjust a normalized TDC output of the first TDC cell prior to adjusting a normalized TDC output of the second TDC cell following the first TDC 45 is a sign-sign LMS algorithm.

The present invention proposes using the existing ADPLL circuitry to do the TDC nonlinearity and gain calibration. In other words, part of the existing ADPLL circuitry is reused by the TDC nonlinearity and gain calibration, which saves area 50 and power. Specifically, all the error information is captured from part of the digital blocks, all non-ideal effects are fixed in the digital domain, and the calibration is very fast and can be operated on-line or at the beginning of every burst. Compared to the conventional design, the proposed calibration 55 mechanism of the present invention does not exhibit phase error hits before each RX/TX packet due to employed iterative operations with small step sizes.

Those skilled in the art will readily observe that numerous modifications and alterations of the device and method may 60 be made while retaining the teachings of the invention. Accordingly, the above disclosure should be construed as limited only by the metes and bounds of the appended claims.

What is claimed is:

1. A method of estimating gain of a time-to-digital converter (TDC) comprising:

10

- capturing a TDC output sample, wherein said TDC output sample is generated by multiplying a TDC code with a TDC normalizing gain;

- calculating a gradient in response to said TDC output sample; and

- utilizing a gain adjusting circuit for adjusting said TDC normalizing gain based on said calculating step.

- 2. The method of claim 1, wherein said adjusting step stochastically reduces error of said TDC normalizing gain.

- 3. The method of claim 1, wherein said gradient is further in response to a reference phase and a variable phase.

- 4. The method of claim 3, wherein said reference phase and said variable phase are set by expected values directly.

- 5. The method of claim 3, further comprising: capturing said reference phase; and capturing said variable phase.

- 6. The method of claim 3, wherein said calculating step calculates said gradient by referring to a slope of said TDC output sample and a slope of a difference between said reference phase and said variable phase.

- 7. The method of claim 1, wherein said TDC is part of an all-digital phase-locked loop (ADPLL).

- 8. The method of claim 1, wherein said adjusting step adjusts said TDC normalizing gain by employing a least mean square (LMS) algorithm.

- 9. The method of claim 8, wherein said LMS algorithm is a sign-sign LMS algorithm.

- 10. A method of calibrating gain of a time-to-digital converter (TDC) comprising:

- capturing a phase error which is derived from combining a TDC output sample, a reference phase and a variable phase;

- calculating a gradient in response to said phase error; and utilizing a gain adjusting circuit for adjusting a TDC normalizing gain based on said calculating step.

- 11. The method of claim 10, wherein said adjusting step stochastically reduces error of said TDC normalizing gain.

- 12. The method of claim 10, wherein said TDC is part of an

- 13. The method of claim 10, wherein said adjusting step adjusts said TDC normalizing gain by employing a least mean square (LMS) algorithm.

- 14. The method of claim 13, wherein said LMS algorithm

- 15. An apparatus of estimating gain of a time-to-digital converter (TDC) comprising:

- a capturing circuit, arranged for capturing a TDC output sample, wherein said TDC output sample is generated by multiplying a TDC code with a TDC normalizing gain; and

- a gain adjusting circuit, arranged for calculating a gradient in response to said TDC output sample, and adjusting said TDC normalizing gain based on said gradient.

- 16. The apparatus of claim 15, wherein said gain adjusting circuit stochastically reduces error of said TDC normalizing

- 17. The apparatus of claim 15, wherein said gradient is further in response to a reference phase and a variable phase.

- 18. The apparatus of claim 17, wherein said reference phase and said variable phase are set by expected values directly.

- 19. The apparatus of claim 17, wherein said capturing circuit is further arranged for capturing said reference phase 65 and said variable phase.

- 20. The apparatus of claim 17, wherein said gain adjusting circuit calculates said gradient by referring to a slope of said

TDC output sample and a slope of a difference between said reference phase and said variable phase.

- 21. The apparatus of claim 15, wherein said TDC is part of an all-digital phase-locked loop (ADPLL).

- 22. The apparatus of claim 15, wherein said gain adjusting 5 circuit adjusts said TDC normalizing gain by employing a least mean square (LMS) algorithm.

- ${\bf 23}.$  The apparatus of claim  ${\bf 22},$  wherein said LMS algorithm is a sign-sign LMS algorithm.

- **24**. An apparatus of calibrating gain of a time-to-digital 10 converter (TDC) comprising:

- a capturing circuit, arranged for capturing a phase error which is derived from combining a TDC output sample, a reference phase and a variable phase; and

- a gain adjusting circuit, arranged for calculating a gradient 15 in response to said phase error, and adjusting a TDC normalizing gain based on said gradient.

- 25. The apparatus of claim 24, wherein said gain adjusting circuit stochastically reduces error of said TDC normalizing gain

- **26**. The apparatus of claim **24**, wherein said TDC is part of an all-digital phase-locked loop (ADPLL).

- 27. The apparatus of claim 24, wherein said gain adjusting circuit adjusts said TDC normalizing gain by employing a least mean square (LMS) algorithm.

- **28**. The apparatus of claim **27**, wherein said LMS algorithm is a sign-sign LMS algorithm.

\* \* \* \* \*