Our staff members (listed in chronological order of joining the group)

Yevhenii Mormul has been a Research Engineer since September 2024. He was our Master student in 2023-2024 working on Noise-shaping pipeline SAR TDC with Dr. Viet Nguyen. He had been with UCD since September 2019. He received his ME Computer and Electronic Engineering in University College Dublin, Dublin, Ireland in 2024.

Yevhenii Mormul has been a Research Engineer since September 2024. He was our Master student in 2023-2024 working on Noise-shaping pipeline SAR TDC with Dr. Viet Nguyen. He had been with UCD since September 2019. He received his ME Computer and Electronic Engineering in University College Dublin, Dublin, Ireland in 2024.

His research interests are:

• Analog and Mixed-Signal IC-Design,

• Data Converters,

• Reference Circuits,

• Frequency Synthesisers,

• Cryogenic Circuitry.

Dennis M. Andrade Miceli worked as R&D Engineer and Cryogenic Lab Manager for Equal1 Labs Ireland between 2019 to 2023, before joining the group to perform the same duties. He previously worked as On-board Electronic Engineer, ASIC Designer, and R&D Engineer for different companies in Mexico, Spain, and Ireland. In recent years he has being focused in R&D projects related to semiconductor-based quantum computing implementations. He is part-time PhD student at UCD since July 2016. His project title is FD-SOI Devices Modelling for QC applications. He received his Bachelor degree from Instituto Tecnológico de Veracruz (Veracruz, México); his MSc degree in Electronic Engineering in 2003 from INAOE (Puebla, Mexico); and his Junior Researcher Certificate from Universitat Politècnica de Catalunya (Barcelona, Spain) on 2010.

Dennis M. Andrade Miceli worked as R&D Engineer and Cryogenic Lab Manager for Equal1 Labs Ireland between 2019 to 2023, before joining the group to perform the same duties. He previously worked as On-board Electronic Engineer, ASIC Designer, and R&D Engineer for different companies in Mexico, Spain, and Ireland. In recent years he has being focused in R&D projects related to semiconductor-based quantum computing implementations. He is part-time PhD student at UCD since July 2016. His project title is FD-SOI Devices Modelling for QC applications. He received his Bachelor degree from Instituto Tecnológico de Veracruz (Veracruz, México); his MSc degree in Electronic Engineering in 2003 from INAOE (Puebla, Mexico); and his Junior Researcher Certificate from Universitat Politècnica de Catalunya (Barcelona, Spain) on 2010.

His research interests are:

• Semiconductor modeling/characterisation,

• Cryoelectronics,

• Quantum Computing Hardware,

• LDOs and BGRs.

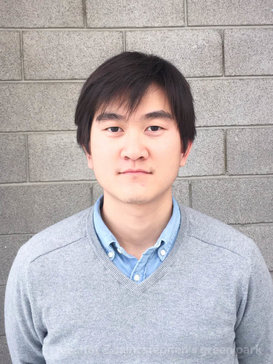

Dr. Teerachot Siriburanon has been a Lecturer/Assistant professor since January 2019. He was a postdoc researcher at UCD between January 2016 to December 2018. He received his PhD and MSc degrees in Physical Electronics from Tokyo Institute of Technology, Japan in 2016 and 2012, respectively. He received his BSc degree from Sirindhorn International Institute of Technology, Thammasat University, Thailand in 2010.

Dr. Teerachot Siriburanon has been a Lecturer/Assistant professor since January 2019. He was a postdoc researcher at UCD between January 2016 to December 2018. He received his PhD and MSc degrees in Physical Electronics from Tokyo Institute of Technology, Japan in 2016 and 2012, respectively. He received his BSc degree from Sirindhorn International Institute of Technology, Thammasat University, Thailand in 2010.

He is a current recipient of a Marie Sklodowska-Curie Individual Fellowship, which is supporting his research on Wave-Locked Loop (WLL) for Frequency Synthesis. He has won the prestigious IEEE Solid-State Circuits Society Predoctoral Achievement Award 2015-2016.

List of publications:

Google Scholar

ORCID

His research interests are:

• ADC-assisted ADPLL,

• Class-C VCO,

• Millimeter-Wave PLLs.

Paulo Vieira was a research engineer and hardware lab manager (both mixed-signal IC and cryogenic) between March 2015 to March 2020. He graduated from Cork Institute of Technology(CIT), Ireland with a Bachelor degree in Electronic Engineering in 2006, and a Master degree in Telecommunications Engineering in 2010. He spent seven years working as an RF Engineer at M/A-COM Technology Solutions in Cork, Ireland, where he found his passion for the RF/Microwaves field, before starting his new challenging job at UCD.

Paulo Vieira was a research engineer and hardware lab manager (both mixed-signal IC and cryogenic) between March 2015 to March 2020. He graduated from Cork Institute of Technology(CIT), Ireland with a Bachelor degree in Electronic Engineering in 2006, and a Master degree in Telecommunications Engineering in 2010. He spent seven years working as an RF Engineer at M/A-COM Technology Solutions in Cork, Ireland, where he found his passion for the RF/Microwaves field, before starting his new challenging job at UCD.